# **FPGAs!? Now What?**

Learning FPGA Design with the XuLA Board

<u>Dave Vandenbout, Ph.D.</u> <u>XESS Corporation</u>

© 2011–2012 XESS, Inc. XESS, the XESS logo, and other designated brands included herein are trademarks of XESS Corporation. All other trademarks are the property of their respective owners.

This document is licensed under the Attribution-ShareAlike 3.0 Unported license, available at http://creativecommons.org/licenses/by-sa/3.0/.

#### FPGAs!? Now What? TUT001 (V1.0) February 28, 2013

The following table shows the revision history for this document.

| Date       | Version | Revision                                                      |

|------------|---------|---------------------------------------------------------------|

| 06/24/2011 | 1.0     | Initial release of Chapters 1-4.                              |

| 07/10/2011 | 1.0     | Added Chapter 5.                                              |

| 08/29/2011 | 1.0     | Added Chapter 6.                                              |

| 03/01/2012 | 1.0     | Added Chapter 7.                                              |

| 09/04/2012 | 1.0     | Changed "chose" to "choose" on page 29.                       |

| 12/30/2012 | 1.0     | Changed link to XSTOOLs setup file.                           |

| 12/30/2012 | 1.0     | Added note to use 32-bit Python and avoid the 64-bit version. |

| 01/24/2013 | 1.0     | Revised Python scripts to use the new XsTools package.        |

| 02/22/2013 | 1.0     | Added Chapter 8.                                              |

# **Table of Contents**

| Ρı | eface                                                |      |   |

|----|------------------------------------------------------|------|---|

|    | Writing Tutorials Sucks Donkeys!                     |      |   |

|    | Here I Go Again                                      |      |   |

|    | What This Is and Is Not                              |      |   |

|    | Really Important Stuff!                              |      |   |

| c. | 1 "I know nothing about FPGAs. Now what?"            | 7    | , |

|    | What Is Programmable Logic?                          | 7    | , |

| _  | 2 "I have no compiler. Now what?"                    | 12   | , |

| ٠. | The Compilation Process: From Schematic to Bitstream |      |   |

|    | Getting and Installing Xilinx ISE WebPACK            |      |   |

| _  | 3 "I have a synthesizer. Now what?"                  |      |   |

| u. | The "Hello, World" of FPGAs: the LED Blinker         |      |   |

|    | Starting a Design in WebPACK                         |      |   |

|    | The Actual Blinker Design (in VHDL!)                 |      |   |

|    | Synthesizing the Blinker (or Not)                    |      |   |

|    | Testing the Logic                                    |      |   |

| _  | 4 "I have a netlist. Now what?"                      |      |   |

| L. | Physical Hardware – the XuLA Board                   |      |   |

|    | Assigning I/O Signals to FPGA Pins.                  |      |   |

|    | Doing the Implementation                             |      |   |

|    | Preparing the Bitstream                              |      |   |

|    | Installing the XSTOOLs Utilities                     |      |   |

|    | Connecting the XuLA Board                            |      |   |

|    | Downloading the Blinker Bitstream                    |      |   |

| _  | 5 "Only 12 MHz! Now what?"                           | 64   | L |

| ٠. | Speed Envy                                           |      |   |

|    | The Digital Clock Manager                            |      |   |

|    | Adding a DFS to the Blinker                          |      |   |

|    | Does It Work?                                        |      |   |

|    | But Does It Really Work?                             | . 69 | ) |

| c. | 6 "No LEDs! No buttons! Now what?"                   | 71   | _ |

| _  | Blinky Envy                                          |      |   |

|    | Monitoring the LED Blinker from the Host PC          | .73  | ż |

|    | Modifying the LED Blinker Project                    | .73  | 3 |

|    | Changing the XuLA Firmware                           |      |   |

|    | PC Software for Talking with the LED Blinker         |      |   |

|    | Putting It All Together                              |      |   |

|    | Testing a Subtractor                                 |      |   |

|    | Two at Once!                                         |      |   |

|    | So What?                                             |      |   |

| C. | 7 "RAMs! Now What!?"                                 |      |   |

|    | Inferring RAM                                        |      |   |

|    | Inferring Distributed RAM                            |      |   |

|    | Inferring Block RAM                                  |      |   |

|    | Integrating RAM into the FSM                         |      |   |

|    | Inferring Multi-Port RAM                             |      |   |

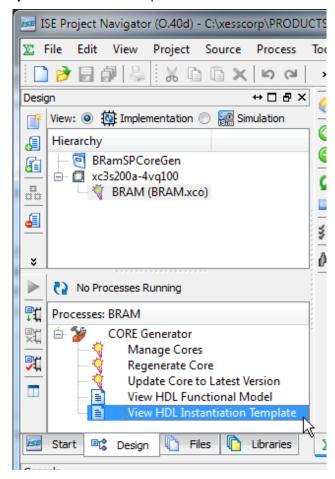

|    | Instantiating RAM                                    |      |   |

|    |                                                      |      |   |

| C.8 "Verilog! Now What!?" | 130 |

|---------------------------|-----|

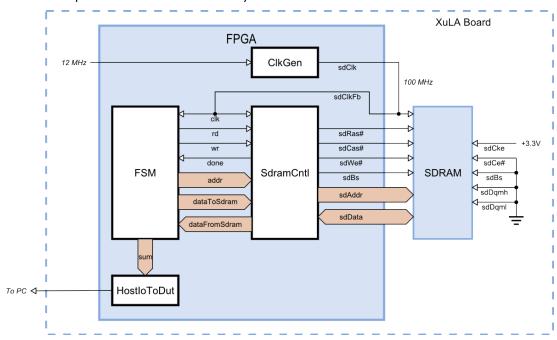

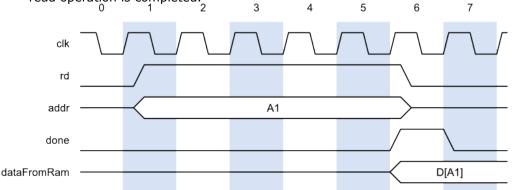

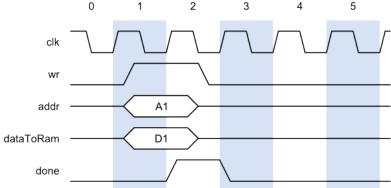

| Simulating SDRAM          | 130 |

# Preface

There are numerous requests in Internet forums that go something like this:

"I am new to using FPGAs. What are they? How do I start? Is there a tutorial and some cheap/free tools I can use to learn more?"

The short answer is "Yes".

The long answer is this book. It will briefly describe FPGAs and then show you how to apply them to your problems using a low-cost board and some free software. My discussion will be oriented towards using Xilinx FPGAs, but most of what I'll say is applicable to other brands of FPGAs.

But first, a little history...

### **Writing Tutorials Sucks Donkeys!**

Yeah, I mean it and I have the experience to back it up.

I've written a lot of documentation over the past twenty years. It's in the nature of my business. I need to write manuals and application notes for my FPGA board customers. I need to generate content for my web pages. I need to write documentation for *myself* just so I can remember what I've done and where I left off.

But the documentation I hate writing most of all is *tutorials*. With a tutorial, you can't assume your reader knows much of anything. You have to build from the ground up. That requires a lot of text, figures, pictures, design examples, etc. And you have to polish and proofread it more thoroughly to make sure its meaning is clear because, if it isn't, someone is going to read it the wrong way and give you a bunch of static about it.

Allow me to take you on a trip down Memory Lane and recount some of the tutorials I've written:

<u>FPGA Workout</u> - 236 pages: I wrote this book back in 1994. It showed how to build electronics using the Intel FLEXlogic FPGAs. (You didn't know Intel built FPGAs? Seems that nobody else did either - they exited the FPGA business around 1995.) I self-published this and had 2000 of them printed. I sold 1500, gave 300 away (one to every EE department in the USA), and watched the last 200 get ground under a bulldozer's tracks in the Wake County landfill (I just couldn't stand having them around anymore).

<u>The Practical Xilinx Designer Lab Book</u> - 300 pages: I wrote this for Prentice Hall back in 1997. They were publishing a student package in cooperation with Xilinx that included this book along with the Foundation FPGA design software. It was a good product at the time. My book covered how to build electronics using Xilinx FPGAs. It

was a real bear working with Prentice Hall after self-publishing my first book. I created and proofread all the text and figures, then Prentice Hall *re-entered all that material using Framemaker* and I had to proofread it all again to catch any transcription errors. (To their credit, there weren't very many. Then again, I wasn't looking *that* hard.)

<u>myCSoC</u> - 213 pages: I wrote this e-book back in 2000. It discussed how to construct electronic systems around the Triscend TE505 chip. (The TE505 combined an 8051 microcontroller with an FPGA on a single chip.) I distributed this book as PDFs from my website and used it as a sales tool for the <u>myCSoC Kit</u>. That came to an end when Triscend went out of business around 2003 and Xilinx gobbled up their dessicated remains. (I still have five-hundred unused TE505 chips from that venture. Anybody want them? Anybody?)

The Practical Xilinx Designer Lab Book Version 1.5 - 450 pages: It wasn't enough to do this once; I went ahead and did a revision! And I added an extra 150 pages of material on - can you guess? - designing electronics using FPGAs. I tried to make a deal with Prentice Hall wherein I would write the print revision for free, and they would grant me the electronic rights to distribute it on the web. This was 1999 and they just couldn't get their heads around this, but they knew they wanted no part of it. Instead, they just paid me \$15,000 for the re-write and told me to drop all the crazy talk. After the book was written, they packaged it with some CDROMs which - instead of containing the Xilinx software - contained test data for an anesthesiology text book! Yeesh, the customer support calls I got! Looking back on it, I realized that all the whipped cream in the world would never make this turd taste any better.

Pragmatic Logic Design With Xilinx Foundation 2.1i - 394 pages: This was what I originally wanted to do for Prentice Hall. An online book with a separate PDF for each chapter. Plenty of room to add as much text and as many figures as were needed because it didn't have to fit into a fixed amount of paper. Easily edited and changed to correct any errors that were found. I got five chapters of this text finished. Then Xilinx released a version of their free WebPACK tools that targeted FPGAs (instead of just CPLDs) and the market for the not-free Foundation software vanished. So did any incentive I had to finish this book.

Introduction to WebPACK X.Y - from 78 pages up to 130 pages: I wrote this tutorial to show how to use the free Xilinx ISE WebPACK software, which had a markedly different user interface than the Foundation software. I wrote a version of the tutorial for WebPACK 1.5 and then 3.1 (these only supported Xilinx CPLDs), then two re-writes for 4.1 (one for CPLDs and another for FPGAs), another re-write for 5.2 (FPGAs only, this time), two re-writes for 6.1 (one targeting the XSA-100 board, and another for the XSB-300E board), one more minor re-write for 6.3 (because of the introduction of the new XSA-3S1000 board), another re-write for 8.1, and a final re-write for ISE WebPACK 10. Xilinx is up to ISE 13 now and, thankfully, it still operates pretty much the same as version 10 because I haven't had the energy to re-write the tutorial. It still serves as a pretty good introduction to the Xilinx software.

All told, that's over two-thousand pages of tutorials. That's a lot, regardless of whether it's mostly roses or shit. What I hated most about doing the tutorials was the boring sameness of it. Each looks like a rehash of the previous one. So I cringe when I think about writing another (hence my three year hiatus from re-doing the WebPACK tutorial).

### Here I Go Again

But it looks like I *am* writing another one. The <u>XuLA board</u> needs a tutorial; it's just too different from any of my other boards and the people who might use it probably have no experience with FPGAs. So they need something to help them get started. But, in order to get *me* started, I'm going to write this tutorial a bit differently so it won't be so boring. Here are the guidelines I set for myself:

*I won't re-invent the wheel.* There's no reason to re-write everything about digital logic design just so I can introduce you to FPGAs – the web is full of good information. I'll add links to good stuff I find to cut my workload and to produce a better text in less time.

*I won't fence it in.* What I really mean is: *steal this book!*. I'm placing the source directory for it on <u>Github</u>. You can copy it, modify it, sell it - I don't care. *I want you to do this!* Please take it, add your own stuff and make it better. All I ask is that you respect the terms of the Creative Commons license I applied to this work. Basically, that means don't remove the names/affiliations of anyone else who worked on this, and provide others with the same rights to it that you got. (But check the actual license to get the fine points.)

*I won't let others fence it in.* I'm using FOSS like LibreOffice and Inkscape to write this book. That removes some barriers for anyone who wants to work on it because they won't have to pay for the tools. And it keeps the source files in non-proprietary formats.

I won't be a prisoner of perfection. I've often held onto things too long before releasing them, trying to remove every error I can find. That's not the case with this book – you'll find spelling and grammar errors, subject/verb disagreements, inconsistent formatting, hand-drawn figures and lots of other stuff. But this won't matter to someone who really needs the material. (For those who do care about the finer points, you can tell me what errors you find and I'll get around to fixing them, or you can get the source and fix them for me.)

*I'll use the right medium for the right message.* Text and figures are great for a tutorial so you can read along while you actually do it. Screencasts and videos are almost always more difficult to follow, especially all the diddling-about with typing text and clicking icons that goes on with FPGA design tools. But there is a place for these, particularly when demonstrating the actual operation of some circuitry.

#### What This Is and Is Not

This book discusses how to use the Xilinx ISE WebPACK software to build FPGA designs for the XuLA FPGA board. Along the way, you'll see:

- How to start an FPGA project.

- How to target a design to a particular type of FPGA.

- How to describe a logic circuit using VHDL and/or schematics.

- How to detect and fix VHDL syntactical errors.

- How to synthesize a netlist from a circuit description.

- How to simulate a circuit.

- How to implement the netlist for an FPGA.

- How to check device utilization and timing for an FPGA.

- How to generate a bitstream for an FPGA.

- How to download a bitstream into an FPGA.

- How to test the programmed FPGA.

- How to detect and fix errors.

I'll also delve into things like:

- How to build hierarchical designs.

- How to build state machines.

- How to build mixed-mode designs using VHDL, Verilog and schematics.

- How to use Digital Clock Managers.

- How to use block RAMs.

- How to use multipliers.

- How to use IP and soft cores.

- How to use external components like SDRAM, VGA, audio, ADC, DAC.

That said, here are some of the things this book will *not* teach you (I may be wrong here; this book isn't even *written* yet, plus who knows what others may add):

- It will not teach you how to use VHDL. There are plenty of good VHDL textbooks already.

- It will not teach you how to choose the best type of FPGA for your particular design. I'm oriented toward using the FPGA on the XuLA board.

- It will not show you every feature of the ISE software and discuss how to set every option and property. This software already has a good help system and extensive manuals, so those should suffice.

In short, this book will get you started using the XILINX ISE software for doing FPGA designs with the XuLA board. After you finish, you should be able to move on to more advanced topics.

#### **Really Important Stuff!**

- Everything for this book is on Github! That includes all the FPGA design examples. I won't be making any zipped archives since they would get out-of-date as changes and corrections are committed to Github. So go to <a href="https://github.com/xesscorp/FpgasNowWhat">https://github.com/xesscorp/FpgasNowWhat</a> if you need anything related to this book.

- All the FPGA design examples in this book are targeted to the XuLA-200 board. You can still use them if you own a XuLA-50 board – just change the target FPGA in the project from xc3s200a-4vq100 to xc3s50a-4vq100.

# **C.1** "I know nothing about FPGAs. Now what?"

## What Is Programmable Logic?

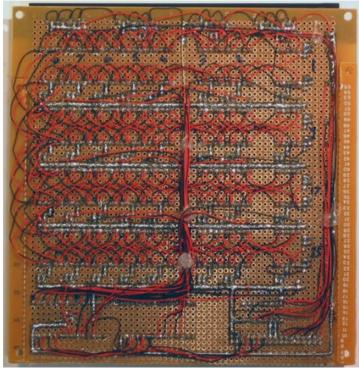

In the beginning (OK, actually in the 60's) there were discrete logic chips. Systems were built from lots of individual ANDs, ORs, flip-flops, etc. with a spaghetti-like maze of wiring between them. It was difficult to modify such a system after you built it. Jeez, after a week or two it was difficult to remember what each of the chips was for!

Spaghetti wiring (courtesy of www.franksworkshop.com.au).

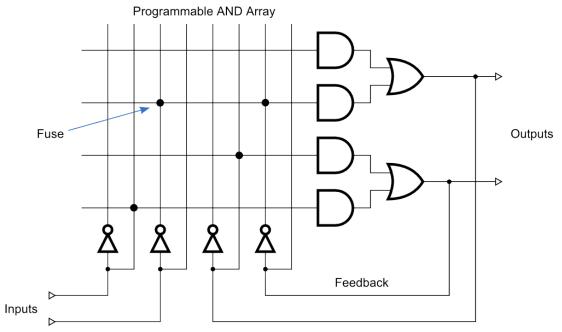

Manufacturing a system like this took a lot of time because each design change required that the wiring be redone which usually meant building a new printed circuit board. The chip makers addressed this problem by placing an unconnected array of AND-OR gates in a single chip called a *programmable logic device* (PLD). The PLD contained an array of fuses that could be blown open or left closed to connect various inputs to each AND gate. You could program a PLD with a set of Boolean sum-of-product equations to perform the logic functions needed in your system. You could change the function of a design by removing the PLDs, blowing a new fuse pattern into them, and then placing them back into the circuit board. This reduced the need to change the actual wiring of the printed circuit boards which held them.

Simple PLDs could only handle up to 10–20 logic equations, so you couldn't fit a very large logic design into just one of them. You had to figure out how to break your larger designs apart and fit them into a set of PLDs. This was time-consuming and meant you had to interconnect the PLDs with wires. The wires were a big no-no because eventually you would make some design change that couldn't be handled just by reprogramming the PLDs and then you would have to build a new circuit board. The chip makers came to the rescue again by building much larger programmable chips called *complex programmable logic devices* (CPLDs) and *field-programmable gate arrays* (FPGAs). With these, you could essentially get a complete system onto a single chip.

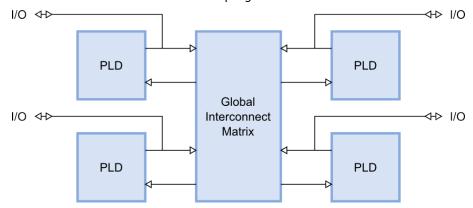

A CPLD contains a bunch of PLD blocks like the one shown above, but their inputs and outputs are connected together by a *global interconnection matrix*. So a CPLD has two levels of programmability: each PLD block can be programmed, and then the interconnections between the PLDs can be programmed.

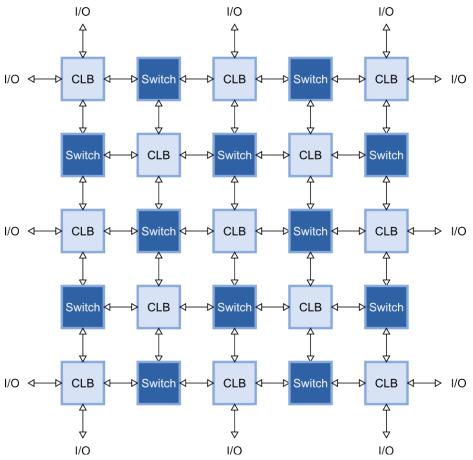

An FPGA takes a different approach. It has a bunch of simple, *configurable logic blocks* (CLBs) interspersed within a *switching matrix* that can rearrange the interconnections between the them. Each logic block is individually programmed to perform a logic function (such as AND, OR, XOR, etc.) and then the switches are programmed to connect the blocks so that the complete logic functions are implemented.

CPLD and FPGA manufacturers use a variety of methods to make the connections between logic blocks. Some make chips with *fuses* or *anti-fuses* that are programmed by

passing a large current through them. These types of CPLDs and FPGAs are *one-time* programmable (OTP) because you can't rewire them internally once the fuses are blown.

Other manufacturers make the connections using pass transistors that are opened or closed by storing a charge on their gate electrodes using a high-voltage pulse. This type of programmable device resembles an EPROM or EEPROM: you can erase it and then place it in a special programmer socket and reprogram it. That's fine unless you have the CPLD or FPGA soldered into a circuit board.

Finally, some manufacturers use static RAM or Flash bits to control the pass transistors for each interconnection. By loading each bit with a 1 or a 0, you can control whether the switch is closed or opened and, therefore, whether two logic elements are connected or not. CPLDs and FPGAs built using RAM/Flash switches can be reprogrammed without removing them from the circuit board. They are often said to be *in-circuit reconfigurable* or *in-circuit programmable*. They are different, however: a Flash-based FPGA always has its programming intact whether it is powered or not, but a RAM-based FPGA will be erased and stop functioning if it ever loses power. Even with this drawback, most FPGAs are RAM-based because the RAMs can be built on the chip using the same manufacturing process as for the CLBs and switches (that makes the chips cheaper to produce). The manufacturers also provide a separate, Flash-based chip that stores the programming switch settings externally and loads it into the FPGA whenever power is applied.

For the rest of this book, we'll concentrate on using RAM-based FPGAs from Xilinx. I'll introduce a little terminology because it will be important later on.

Within the CLBs of an FPGA are *look-up tables* (LUTs) that perform the actual logic operations. These are usually built as small RAMs that are loaded with a truth table. For example, an eight-bit RAM can perform a three-input AND operation if it is loaded as follows:

If the inputs for the AND gate are applied to the address pins of the RAM, then the output of the RAM will only be 1 when location 7 = 111 is selected. This is exactly how a three-input AND gate would operate. By setting the contents of the RAM in the right way, you can perform *any* logic function of three binary inputs. (Modern FPGAs use LUTs with four to six inputs.)

The output of a LUT can be used directly as an input to another LUT to make more complicated logic functions. Or it can be stored in a flip-flop for later use (there's usually at least one register for each LUT).

The switching matrix routes all the signals between the LUTs and registers and also to the I/O blocks (IOBs) around the perimeter of the FPGA chip. The IOBs connect selected internal signals of the FPGA to the outside world and contain special analog circuitry to

adjust the input and output voltage levels, insert small delays, and handle single-ended or differential signaling.

Over time, other types of more specialized circuit blocks have found their way into FPGAs: blocks of RAM, multipliers and DSP blocks, delay-locked and phase-locked loops, gigabit serial transceivers, and even complete microprocessors. But, at least when you're starting off, your main concern will be the LUTs and registers. These are the equivalent of the program and data memories in a processor: the values in the LUTs and flip-flops determine how your logic circuit functions, and your design must fit into the available number of LUTs and flip-flops within your target FPGA.

Also, like a microprocessor, you need a way to write programs for your FPGA. That's the subject of the next chapter.

# C.2 "I have no compiler. Now what?"

### The Compilation Process: From Schematic to Bitstream

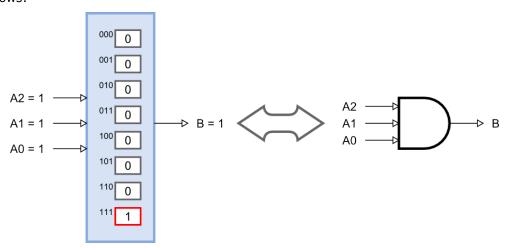

As you can imagine, figuring out which bits to set in the LUTs and the switching matrix in order to create a logic circuit is quite a chore. Not many people would want to delve into the details of this (probably the same ones who like to program in assembly). That's why the FPGA manufacturers provide development software that compiles a high-level description of a logic design and outputs a *bitstream* which sets the FPGA configuration bits appropriately.

The process the development software goes through to compile a design into a bitstream is depicted in the figure on the next page. Here's what happens:

- 1. You enter a description of your logic circuit using a *hardware description* language (HDL) such as VHDL or Verilog. Or you can also draw your design using a schematic editor. Or you can use a combination of the two.

- 2. A *logic synthesizer* transforms the HDL into a *netlist*. The netlist is just a description of the various logic gates in your design and how they are interconnected. (A schematic is already pretty close to a netlist, so it doesn't need as much work done on it as the HDL code.)

- 3. The *implementation phase* employs three different tools. A *translator* merges together one or more netlists along with any *design constraints* (don't worry about those now). This is fed to a *mapper* that combines gates in the netlist into groups that will fit efficiently into the LUTs of the FPGA. The gate groupings are sent to the *place & route tool* that assigns them to LUTs at various locations in the FPGA and then determines how to connect them together using the routing resources (wires) in the switching matrix. This part takes the most time as finding a placement that can be routed efficiently requires a lot of computation.

- 4. A *bitstream generator* takes the output of the implementation phase, combines it with a few other configuration settings, and outputs a binary bitstream. This bitstream (which, depending upon the size of the FPGA, can be many megabits in length) contains the truth-tables that will be loaded into the RAM of every LUT and the connection settings for the wiring matrix that will connect them.

- 5. At this point, a bitstream is just a bunch of 1s and 0s in a file on the computer. The *downloader* will transfer this file into a physical FPGA chip. In most cases, this chip is already mounted on a circuit board where it waits for the bitstream that will make it perform its intended function.

After downloading, you can apply patterns of input signals (or *test vectors*) to the I/O pins of the FPGA to check the operation of your design. This is often an effective way to do testing, but sometimes it's difficult to set up a particular combination of signals and look deeply into the internals of your design to see why it may not be performing as you intended.

If that's the case, you can use a *simulator* to try out test examples and see how your circuit reacts before you actually load it into an FPGA. There are several places in the design flow where you can perform a simulation. If you capture the netlist before it enters the implementation tools, you can run a *logic simulation* that only tests the logical operations of the gates in your circuit. Such simulations are good for debugging the basic functions of your design.

As you tap the design flow at points further downstream, the netlist is augmented with more and more information about how your design will be placed into the FPGA. This allows you to perform a more realistic *timing simulation* that incorporates the effects of gate and wiring delays on the operation of your circuit. This is useful for detecting errors caused when signals arrive too quickly or slowly at their destinations. Because of this extra level of detail, timing simulations take longer to run than a pure logic simulation.

At this point you know the steps in the compilation process, but what you really want to know is how to get a compiler. That comes next.

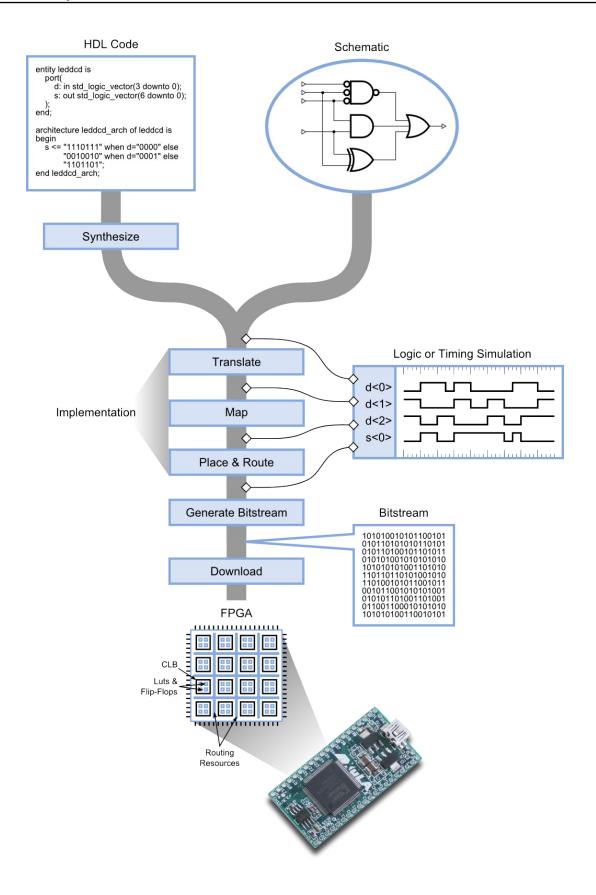

#### **Getting and Installing Xilinx ISE WebPACK**

Xilinx develops and sells their ISE FPGA tools, and they also distribute a free version called WebPACK. WebPACK won't generate bitstreams for the *really* large FPGAs and it lacks some special-function design tools, but it will perform all the functions I discussed in the previous section for FPGAs containing up to 75,000 LUTs with hundreds of I/O pins. That will be more than sufficient for this tutorial.

To get WebPACK, just do a search for "xilinx webpack download" (use Google, Bing, whatever). If you click on the first link you get, it will probably take you to the page shown below. The latest version of the software should be highlighted along the left side (it's currently 13.1). Click on the <u>Full Installer</u> link for whatever operating system you're using (either Windows or Linux, currently).

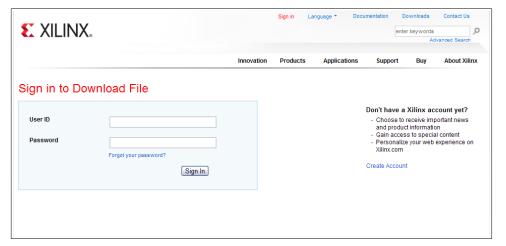

Before the download begins, you'll be presented with a sign-in screen. If you don't already have a Xilinx account, you'll have to create one. Then sign in using your ID and password.

Then you'll have to go through a screen that verifies all your contact information. Click on the **Next** button at the bottom and your download will begin. Now be prepared to wait an hour or two as the file is about 4 GB.

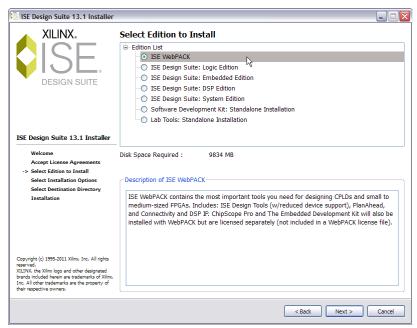

After the archive is downloaded, you can unpack it (that'll take a ten minutes) and run the installer. You'll go through a set of installation screens. Make sure you choose the WebPACK edition unless you want to pay money for one of the others or are willing to accept a time-limited license (usually 30 days).

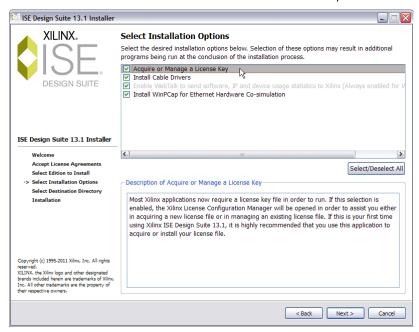

Also make sure to select the option to get a license key. (Yes, you will need a key even though WebPACK is free. The WebPACK license is not time-limited, so it will never expire.)

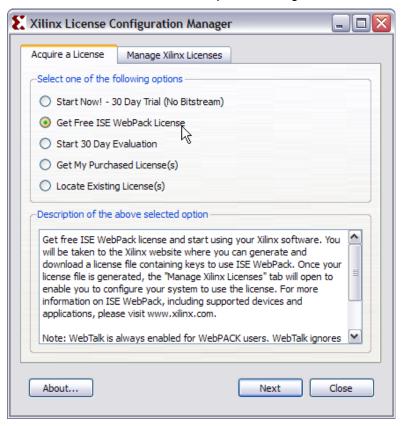

When the installation is almost done (that takes about 45 minutes), you'll see this screen appear. Select the WebPACK license as the one you want to get and click **Next**.

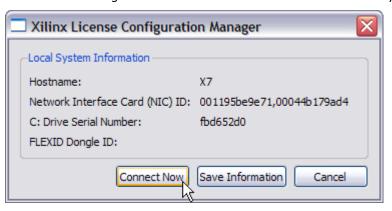

Then you'll get a screen showing the information that will be associated with your license.

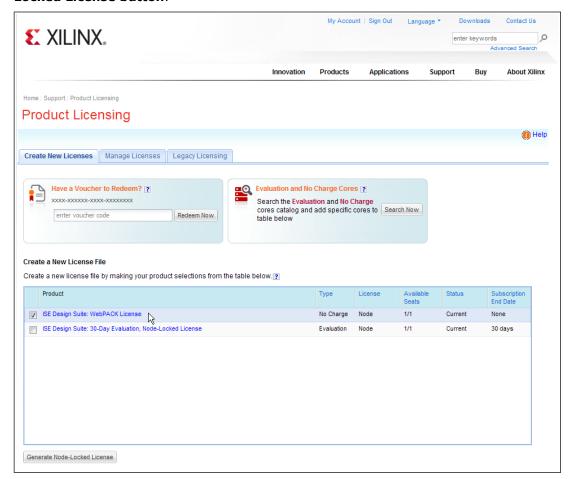

Click the **Connect Now** button to start the license generation process. Once you do, your browser will open a window to Xilinx and you'll have to login using your account information (again). Then you'll have to verify your contact information (again). Finally, you'll get to this screen. Select the WebPACK checkbox and click on the **Generate Node Locked License button**.

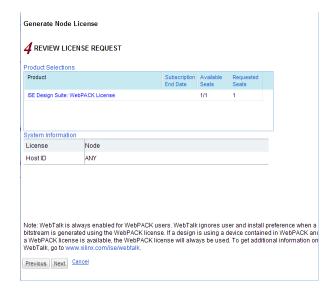

Next you'll see a couple of confirmation screens like the following:

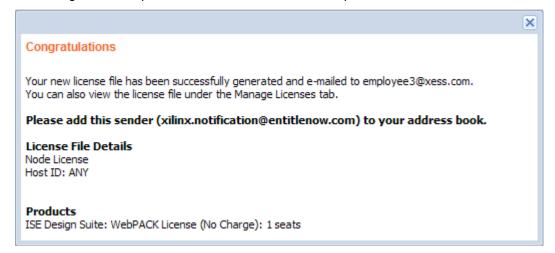

After clicking the **Next** button in the final confirmation screen, you'll get an acknowledgment that your license has been emailed to you.

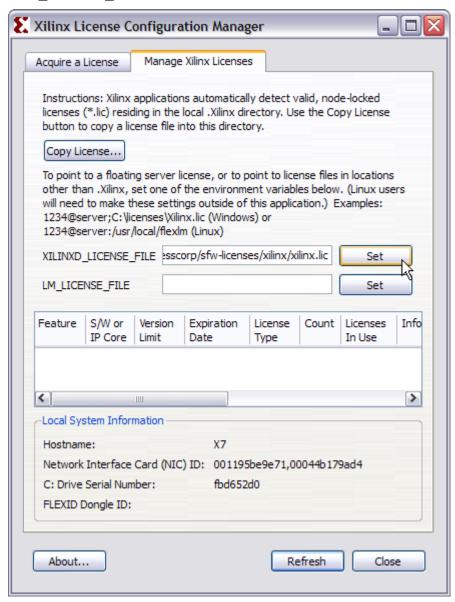

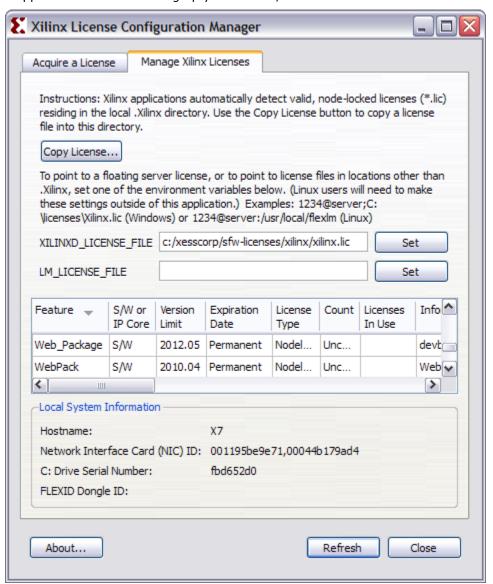

Once you've received the email, save the attached license file somewhere (but remember where you put it!). Then go back to the **Xilinx License Configuration Manager** screen and click on the **Manage Xilinx Licenses** tab. Enter the location of your license file into the **XILINXD\_LICENSE\_FILE** field and click on the **Set** button.

Once you click on the **Set** button, a list of the enabled features in the WebPACK software should appear. You're done setting up your license, so click on the **Close** button.

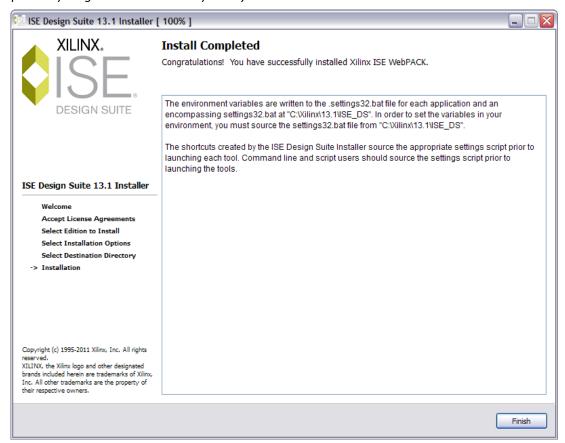

You can also click on the **Finish** button in the final window of the WebPACK installer. (You probably forgot all about that by now.)

The WebPACK installation is done! You've got your party dress on, now it's time to dance!

# C.3 "I have a synthesizer. Now what?"

## The "Hello, World" of FPGAs: the LED Blinker

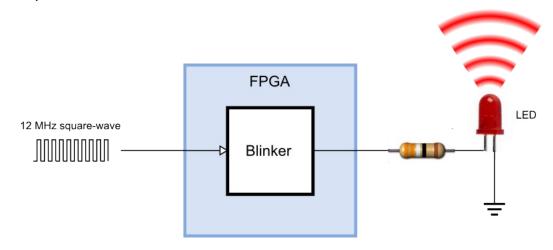

Now that your WebPACK tools are installed, it's time to do your first FPGA design: an LED blinker. This blinker will take a 12 MHz square-wave clock signal (you'll see why in the next chapter) and slow it down so an LED will turn on-and-off about once per second (i.e., 1 Hz).

## Starting a Design in WebPACK

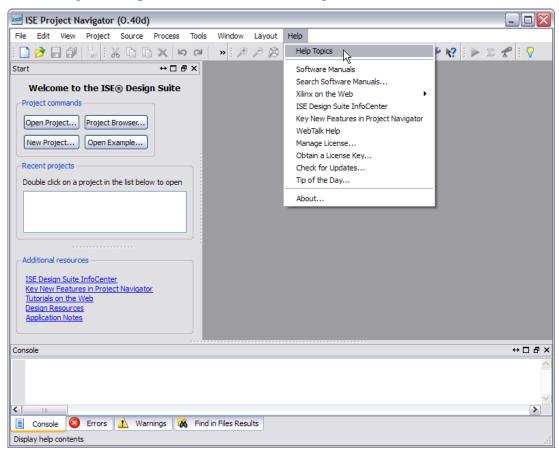

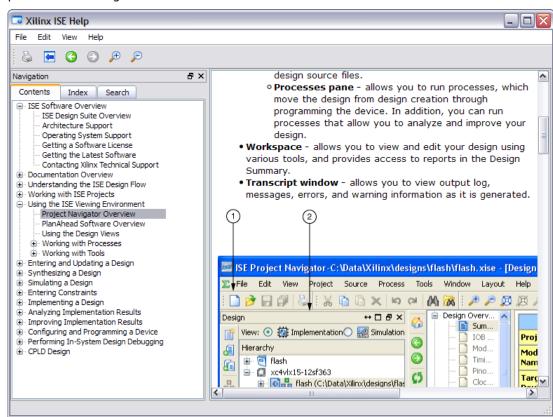

You start WebPACK by double-clicking the ISE 13.1 icon on the desktop. This will bring up an ISE Project Navigator window like the following one.

If this is your first time using Navigator, it's a good idea to click on the **Help** button and bring up the **Project Navigator Overview**. Read this to get an idea of what all the panes in the Navigator window are used for.

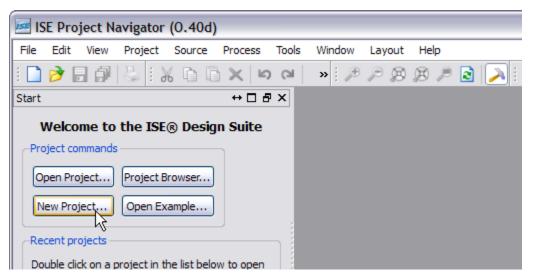

To start your LED blinker design, click on the **New Project...** button in the Navigator window.

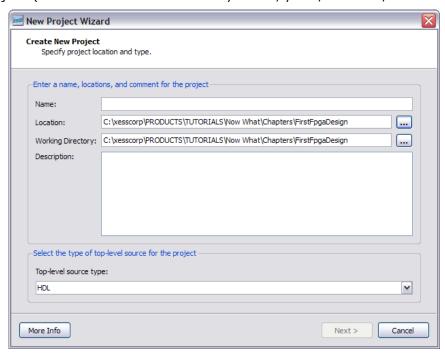

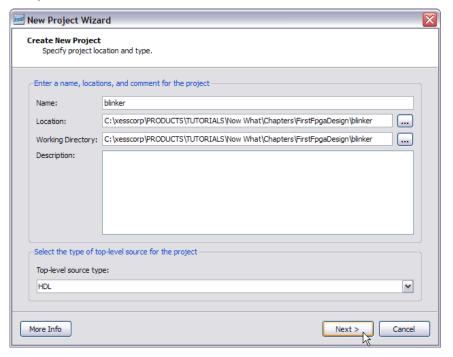

This will bring up the **New Project Wizard**. The first thing to do is select a location for your project. (The screenshot below shows my choice; yours, of course, will be different.)

Then type in a name for the project. I've chosen "blinker". (Notice how the project name is added to the end of the location you set previously. A folder with this name will be created there.) Then click on the **Next** button.

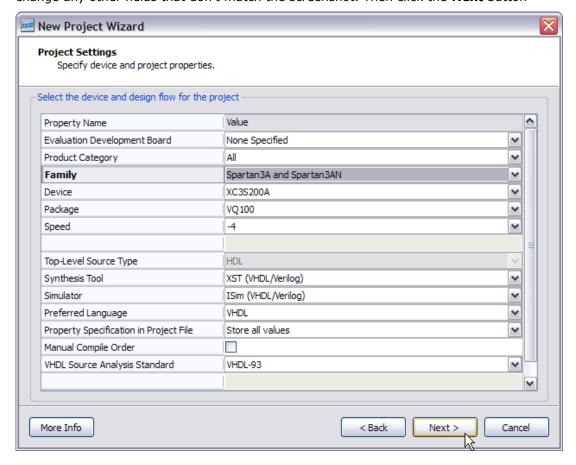

The next screen that appears is used to select the type of FPGA you want to use for your design (i.e., the *target*). Set the **Family**, **Device**, **Package** and **Speed** fields as shown below. (This sets up your design for the particular FPGA used on the XuLA board.) Also, change any other fields that don't match the screenshot. Then click the **Next** button

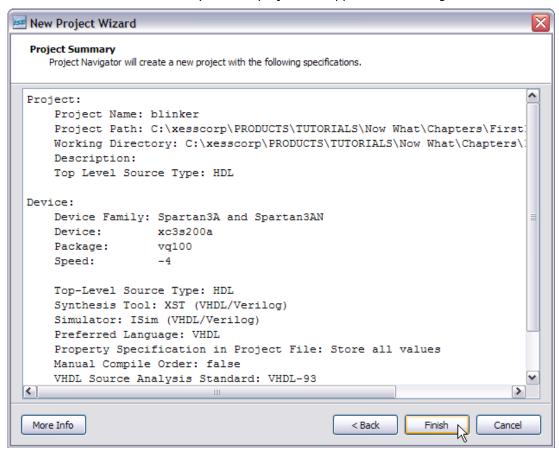

Now you'll get a summary of the information you've entered about your blinker design. Click on the **Finish** button and your new project will appear in the Navigator window.

# The Actual Blinker Design (in VHDL!)

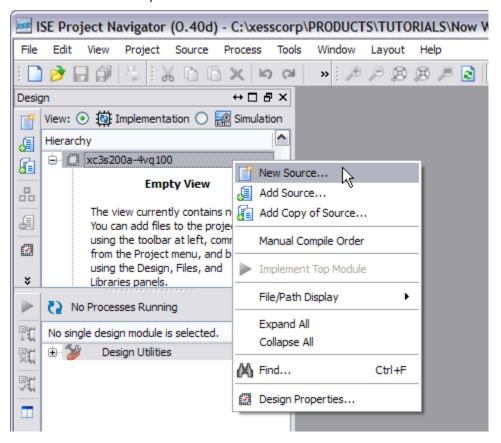

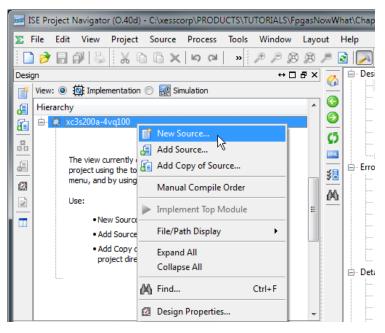

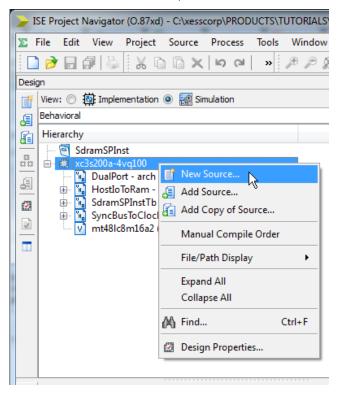

At this point, your project exists, but it doesn't do anything. It's time to enter the *source* information that describes how the blinker operates. In the Navigator window, right-click on the FPGA identifier (xc3s200a-4vq100 in this design) in the **Hierarchy** pane and select **New Source...** from the drop-down menu.

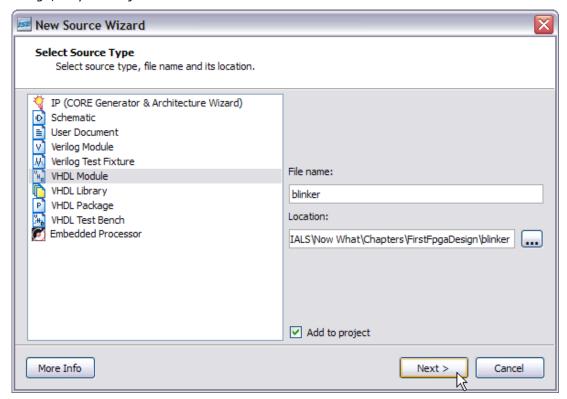

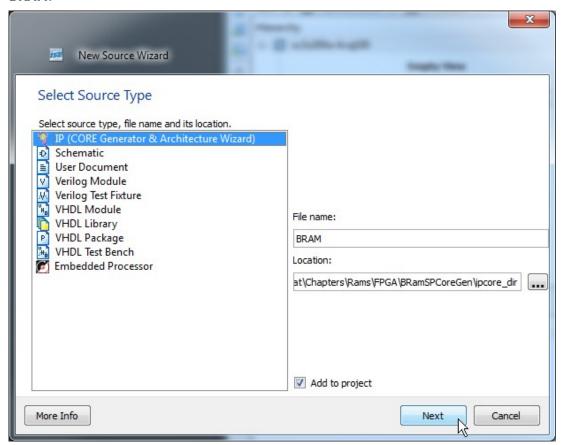

The **New Source Wizard** window appears. Here, you can select how you want to describe your design. For example, you could create the blinker from logic gates using schematics. Or maybe there is already a pre-built blinker circuit provided as an *intellectual property* (IP) core (don't bet on it!). But for this design, I will choose to use VHDL. VHDL (or Verilog, they're really quite similar) lets you describe the operations of logic designs using a high-level language. So, select **VHDL Module** from the list of source types. Then type a name for the VHDL source file. There will only be one for this simple design, so you can just name it "blinker". Then click on the **Next** button

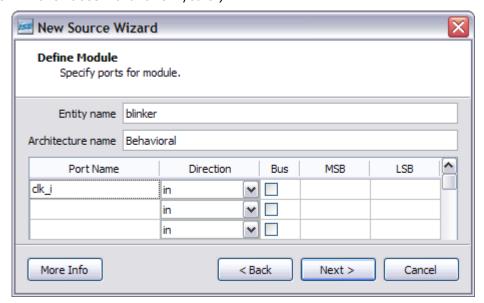

The next window that appears lets you define the input and output ports for the blinker design. Type "clk\_i" into the first **Port Name** field. This will be the input for the 12 MHz clock signal. (The "\_i" suffix on the port name is not necessary. I just use this notation to indicate which ports are inputs. That can help if I'm trying to figure out how an old design works if I haven't seen it for a few years.)

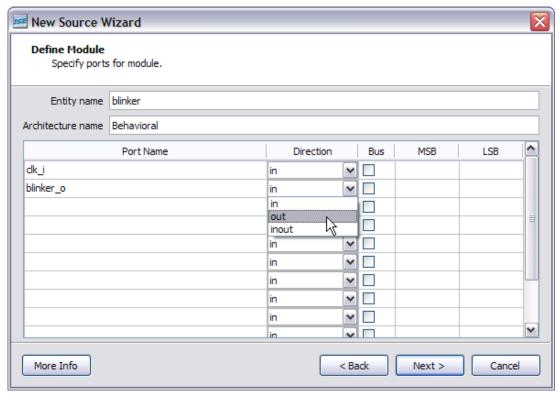

Then you can add the output that drives the LED. Name this "blinker\_o" and set it to be an output using the **Direction** drop-down list as shown below.

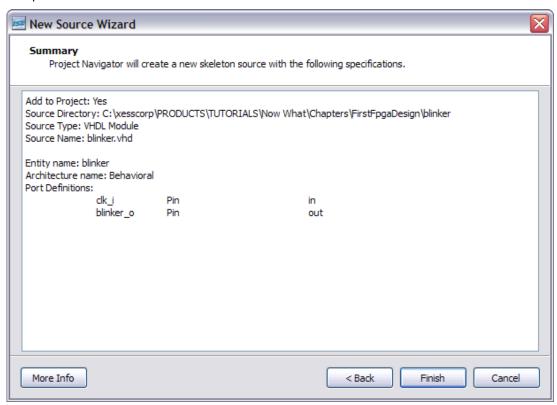

That's all the inputs and outputs you need. Click on the **Next** button and you'll get a summary of your VHDL module. No surprises there! Click on the **Finish** button to complete the module.

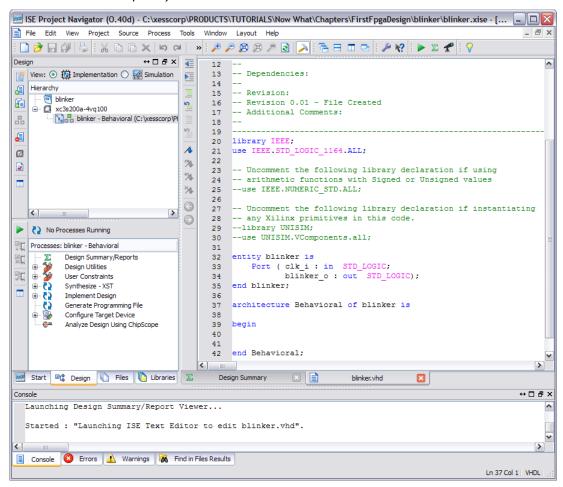

Now you should see the contents of your blinker VHDL module in the Navigator workspace pane to the right. (If you don't see it, click on the **blinker.vhd** tab along the bottom of the workspace.)

Most of the blinker.vhd file is comments, but there are a few spots you should look at:

- **Lines 20-21**: These two lines open the STD\_LOGIC\_1164 *package* of the IEEE library. This library includes a bunch of useful functions and definitions and you'll see it included in most VHDL designs.

- **Lines 32-35**: This is the *entity* section of the blinker where all the inputs and outputs are declared. This is like the skin of the module which defines how everyone on the outside will see the blinker.

- **Lines 37-42**: This is the architecture section of the blinker where all the functions are defined. This portion is the guts of the design where the inputs are taken in, worked on, and then the result is passed out through the outputs. Notice, however, that the architecture section is conspicuously empty the blinker will do nothing at this point!

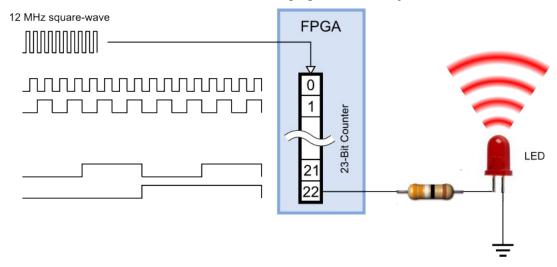

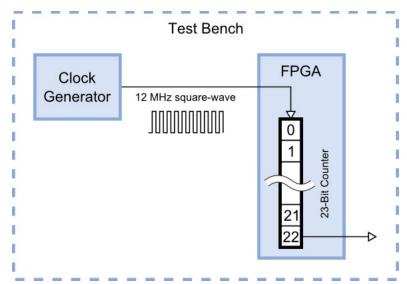

So it's pretty clear that you need to put something into the architecture section to make the blinker work. A <u>counter</u> is a common component for reducing a 12 MHz clock down to a 1 Hz waveform. Why? Because a binary counter increments whenever the clock pulses and it goes through a binary sequence such as 000, 001, 010, 011, 100, 101, 110, 111, ... If you look, you'll see that each bit of the counter pulses at half the frequency of the previous bit. (Look <u>here</u> for a better illustration of how binary counters work.) So if you build a counter with a enough bits, you can divide the 12 MHz clock downto 1 Hz.

But how many counter bits do you need? Well, a one-bit counter would divide the clock by

two down to 6MHz. A two-bit counter would divide it by four downto 3 MHz. An N-bit counter would divide by  $2^N$ . So what value of N would divide by 12,000,000? It turns out you can't get exactly 12,000,000, but you can get 8,388,608 if you use N=23, or you can get 16,777,216 with N=24. For no particularly good reason, let's use N=23.

Here's a more detailed view of the blinker design given what we just covered:

The 23-bit counter is incremented on the rising edge of the 12 MHz input clock. Bit 0 of the counter outputs a 6 MHz signal. (Why do we count the counter's bits starting from zero? BECAUSE THAT'S HOW ENGINEERS DO THINGS!!) Bit 1 outputs a 3 MHz signal. By the time we reach the final bit of the counter (bit 22), the signal is pulsing at a rate of 12,000,000 / 8,388,608 = 1.43 Hz. This bit is output from the FPGA and is connected to the LED. So the LED flashes once every 0.7 seconds.

Now all you have to do is describe this 23-bit counter in VHDL. That's not too hard. Here it is:

```

36

37

architecture Behavioral of blinker is

38

signal cnt r : std logic vector(22 downto 0);

39

begin

40

41

process(clk_i) is

42

begin

if rising_edge(clk i) then

43

cnt r <= cnt r + 1;

44

end if;

45

46

end process;

47

48

blinker_o <= cnt_r(22);

49

end Behavioral;

50

51

52

< III

>

Design Summary (Synthesized)

blinker.vhd

\leftrightarrow \Box \Box \times

```

Here's what's going on in the architecture section:

Line 38: This is the declaration for the register (cnt r) that holds the 23-bit count

value. The value is represented as a vector of 23 binary digits with indexes from 22 down to 0. (I used the "\_r" suffix to remind myself that this is a register.)

**Lines 41-46**: This is a process that is triggered every time the clock input changes its value, either on the rising edge (i.e., from  $0 \Rightarrow 1$ ) or the falling edge ( $1 \Rightarrow 0$ ). Within the process is an if statement that increments the value in the count register only on the rising edges of the clock.

**Line 48**: The most-significant bit of the count register is attached to the blinker output. That's all there is to it. Now let's see if it passes through the synthesizer.

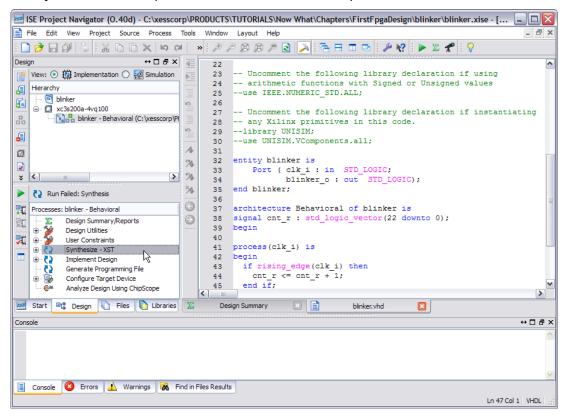

## Synthesizing the Blinker (or Not)

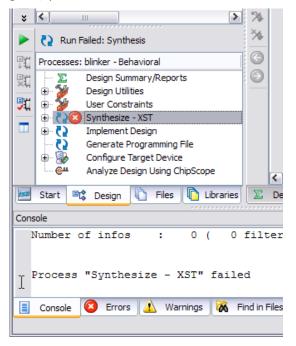

To run the synthesizer, left-click on the **blinker** icon in the Hierarchy pane. Once you do that, you should see a list possible operations appear in the **Process** pane. Double-click the **Synthesize** – **XST** process icon to start the VHDL synthesizer.

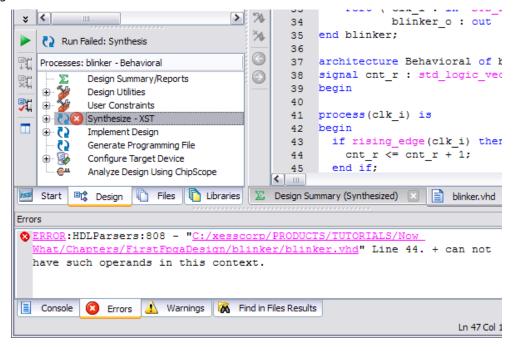

Within a few seconds you should see the results of the synthesis, and it isn't good. In the bottom portion of Navigator, you'll see this:

That red "X" is never a good sign. In this particular instance, it means the synthesizer has run into an error. As to what the error is, click on the **Errors** tab of the Transcript window to get the details.

The synthesizer is telling you that the "+" operator cannot process its operands. In other words, there is no operation defined for adding an integer to a std\_logic\_vector. That's not a big problem; you just have to include the package that defines this particular addition operator. It turns out it's defined in the STD\_LOGIC\_UNSIGNED package, so just add what's shown on line 22 to the VHDL like so:

```

-- Revision 0.01 - File Created

17

- Additional Comments:

18

19

library IEEE;

20

use IEEE.STD LOGIC 1164.ALL;

21

use IEEE.STD LOGIC UNSIGNED.ALL;

22

23

-- Uncomment the following library declaration

24

-- arithmetic functions with Signed or Unsigned

25

--use IEEE.NUMERIC STD.ALL;

26

27

-- Uncomment the following library declaration

28

-- any Xilinx primitives in this code.

29

--library UNISIM;

30

--use UNISIM.VComponents.all;

31

32

entity blinker is

33

Port ( clk i : in STD LOGIC;

34

35

blinker o : out STD LOGIC);

36

end blinker;

37

architecture Behavioral of blinker is

38

signal cnt r : std logic vector(22 downto 0);

39

>

Design Summary (out of date) 🖂 🖹 blinker yhd 🔯

```

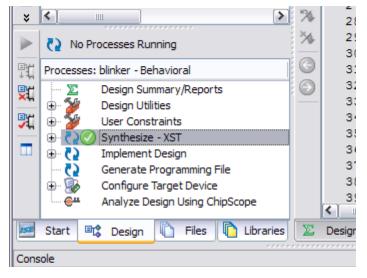

Save the file and double-click the **Synthesize – XST** process icon again. Now you should see the synthesis completed successfully.

Now you have a netlist synthesized from your VHDL file. But does it work?

## Testing the Logic

Before you charge off and run the implementation tools so you can blast your design into an FPGA to see if it works, it might be wise to take a little time to do a logic simulation. (Now I admit I always run the implementation tools and blast my designs into an FPGA to see if it works before even considering running a simulation, but you shouldn't emulate my bad habits.)

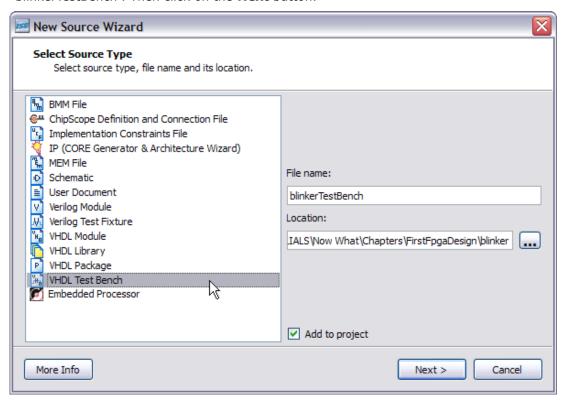

In order to simulate your design, you need something to exercise its inputs and watch its outputs. For your blinker design, you need an external wrapper that will apply a signal to the clock input and watch the output to see what it does. This wrapper is called a *test bench*.

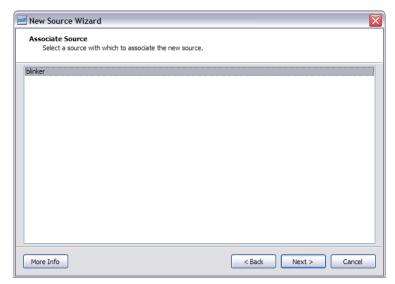

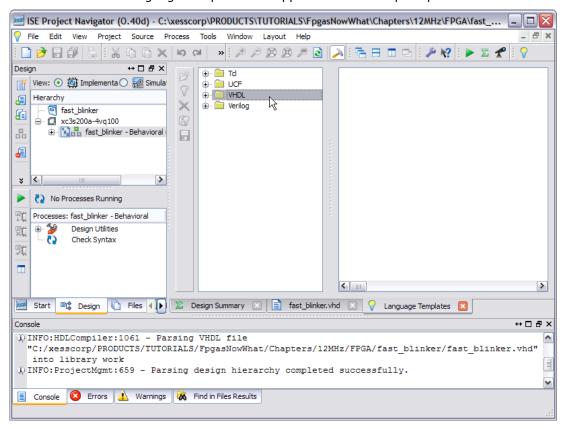

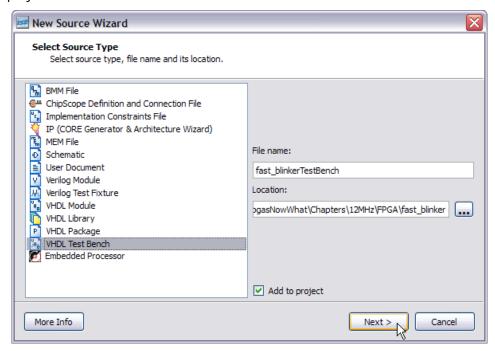

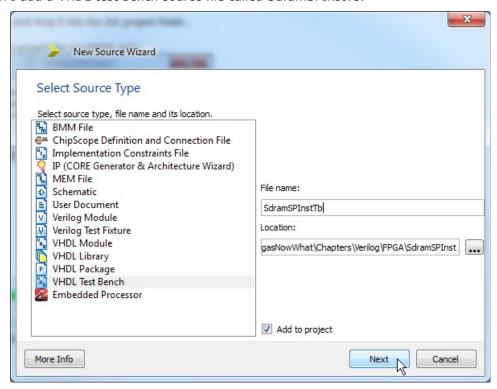

So you need to add a test bench to your project. To do this, right-click on the FPGA identifier in the **Hierarchy** pane and select **New Source...** in the pop-up menu. In the New Source Wizard window, select the VHDL Test Bench as the source type and name it "blinkerTestBench". Then click on the **Next** button.

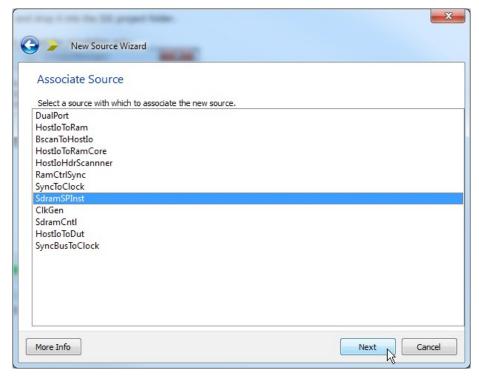

The next window that appears asks you to select a source file to associate with your test bench. Essentially, this is asking for the module to wrap the test bench around. There's only one module in your design (blinker), so that's your only choice. Click **Next** and move on.

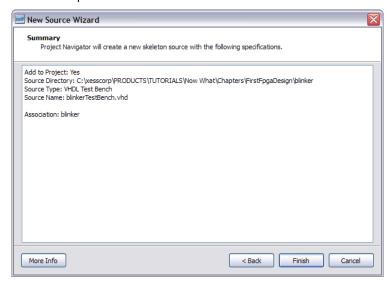

You'll get a summary screen about the choices you've made. Again, no surprises! Click on the **Finish** button to complete the addition of the test bench module.

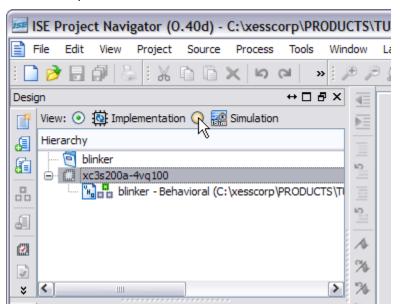

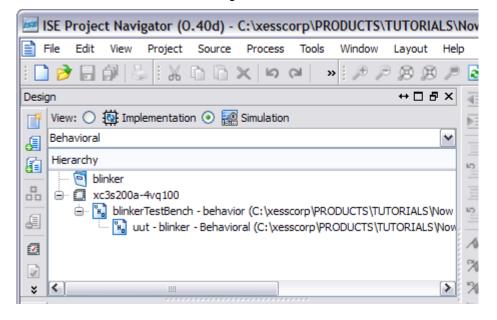

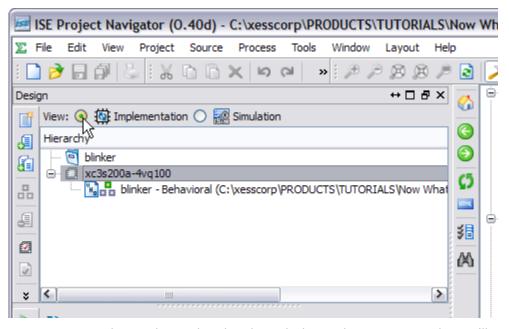

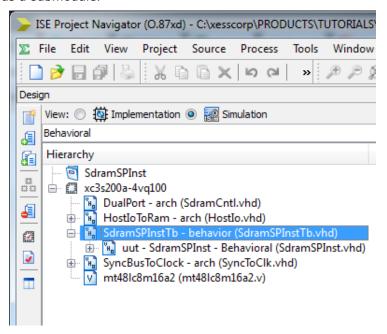

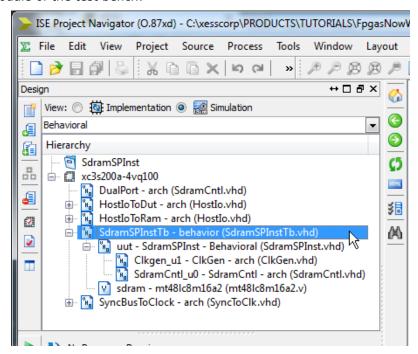

When you return to the Navigator screen, take a look at your **Hierarchy** pane. Where's the test bench you just added? It's not actually missing, it just doesn't show up in the **Implementation** view of your project. In order to see the test bench, you have to select **Simulation** in the **View** pane like so:

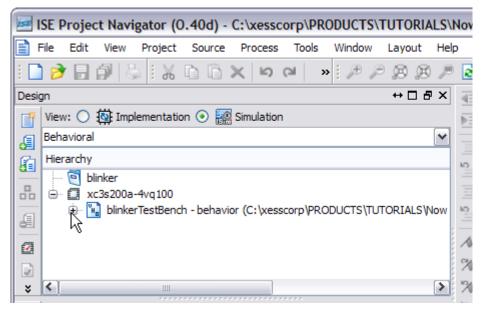

Once you select the Simulation view, the blinkerTestBench file shows up in the **Hierarchy** pane. The important point to note here is that the test bench module is not something that will ever be implemented and downloaded to the FPGA. In fact, it might be difficult or impossible to do so because the test bench might contain language constructs that are difficult or impossible to build in the FPGA (like accessing a file on the host computer to store test results). The test bench serves only to help in exercising the actual modules that will end up in the FPGA. Speaking of which, where is the blinker module?

By clicking on the "+" sign next to the blinkerTestBench icon, you can see the blinker module is displayed as a submodule contained in the blinkerTestBench module. The blinker module is labeled "uut" in the test bench. This stands for "unit under test" to indicate the blinker module is what is being tested.

Now you'll want to double-click the blinkerTestBench file so you can add the VHDL code for exercising the blinker module. (It turns out you won't have to do much.) In the initial portion of the test bench file, you'll see the inclusion of the IEEE library (lines 28-29) and the entity declaration for the blinkerTestBench module. Notice that the entity section lists no inputs or outputs. That's because the test bench completely wraps the UUT and no inputs or outputs pierce the wrapper – everything happens inside the test bench.

```

w What\Chapters\FirstFpgaDesign\blinker\blinker.xise - [blinkerTestBench....

_ || 🗆 || 🗙

_ & X

28

LIBRARY ieee;

^

USE ieee.std logic 1164.ALL;

29

30

31

- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

32

--USE ieee.numeric std.ALL;

33

34

ENTITY blinkerTestBench IS

35

END blinkerTestBench;

36

37

```

The architecture section (see the following figure) instantiates the blinker module as the UUT, connects to its inputs and outputs, and then drives the inputs. Here are the details:

- **Lines 42-47**: This is a component declaration so the rest of the code knows what the interface to the blinker module looks like. Hence, it looks very similar to the blinker module entity section.

- **Lines 50-54**: Signals internal to the test bench are declared that will be connected to the input and output ports of the blinker module.

- **Line 57**: The period of the clock input is defined with the default value of 10 ns. Since you want to simulate the blinker with an input clock of 12 MHz, this constant should be changed to 83.3 ns.

- **Lines 62-65**: The blinker module is instantiated here. Its input and output ports are connected to the similarly-named signals declared previously.

- **Lines 68-74**: The clock signal is generated in by this process. The clock signal is forced to 0 and the process waits for half of the clock period. Then the clock is raised to 1 and the process waits for the remaining half of the clock period. Then the entire sequence repeats forever.

- **Lines 78-88**: Test vectors for other inputs to the UUT can be generated in this process. Since the blinker module only has a clock input, there's nothing for this process to do. So leave it unchanged.

```

ARCHITECTURE behavior OF blinkerTestBench IS

39

40

-- Component Declaration for the Unit Under Test (UUT)

41

COMPONENT blinker

42

PORT (

43

44

clk i : IN std logic;

blinker_o : OUT std_logic

45

46

47

END COMPONENT;

48

49

--Inputs

50

signal clk_i : std_logic := '0';

51

52

--Outputs

53

signal blinker o : std logic;

54

56

-- Clock period definitions

57

constant clk i period : time := 10 ns;

58

59 BEGIN

60

-- Instantiate the Unit Under Test (UUT)

61

uut: blinker PORT MAP (

62

clk i => clk i,

63

blinker o => blinker o

64

65

);

66

-- Clock process definitions

67

clk i process :process

68

begin

69

clk_i <= '0';

70

wait for clk i_period/2;

71

clk_i <= '1';

72

wait for clk_i_period/2;

73

74

end process;

75

76

77

-- Stimulus process

stim proc: process

78

79

begin

80

-- hold reset state for 100 ns.

81

wait for 100 ns;

82

wait for clk_i_period*10;

83

84

85

-- insert stimulus here

86

87

wait;

88

end process;

89

90 END;

<

```

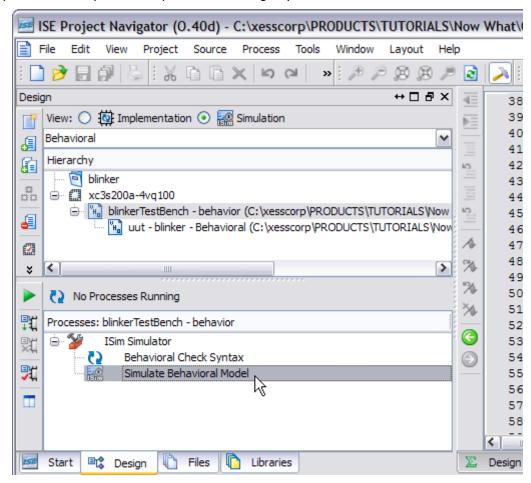

The test bench looks like it's ready, so it's time to run a simulation. Click on the blinkerTestBench entry in the Hierarchy pane, and then double-click the Simulate Behavioral Model in the Processes pane. (There's no need to run the Behavioral Check Syntax since only the clock period was changed.)

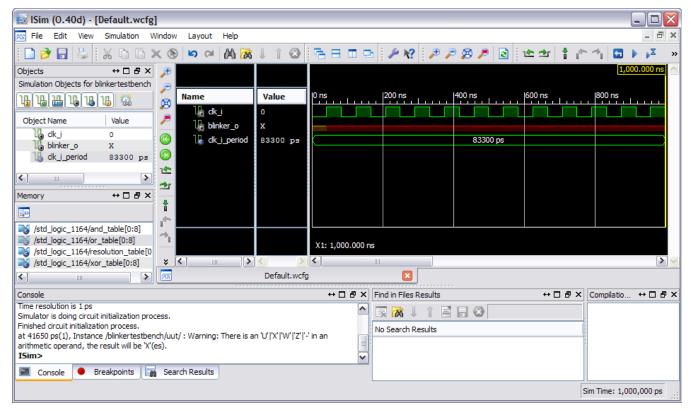

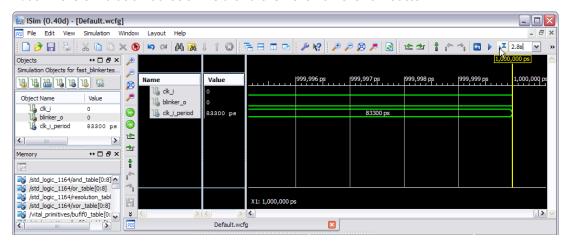

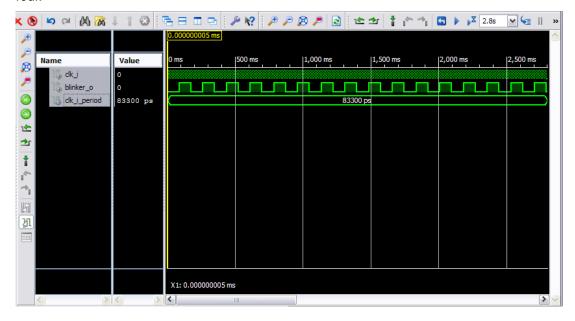

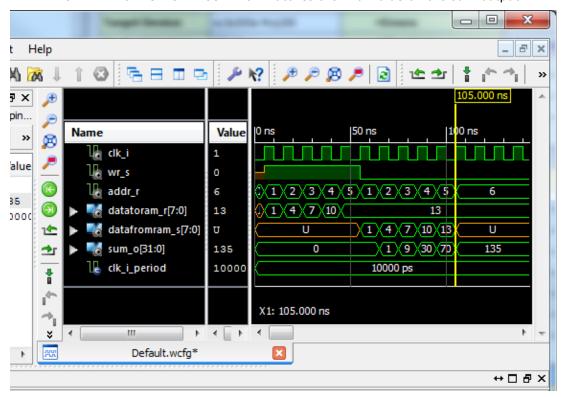

The ISim window will appear and display the results of a 1  $\mu$ s simulation run. (Click on the **View**  $\Rightarrow$  **Zoom**  $\Rightarrow$  **To Full View** menu item to make the entire waveform visible.)

Although the simulation only ran for a microsecond, there's already something wrong about it. The blinker\_o output remains in an unknown state (signified by an "X") even after the clock signal has pulsed twelve times. It should have gone to one or zero after the first clock pulse.

This is a symptom of an initialization problem. In this case, the counter register is not initialized to a known value at the start of the simulation. Since the counter value is unknown, the simulator can't determine the next value it should contain when a rising clock edge occurs. So all the counter bits stay in an unknown state, including the counter bit attached to the blinker\_o output.

How do you fix this? Well, the *right* way would be to build some reset circuitry in the blinker module that sets the counter register to zero when a reset input is triggered. Then the test bench could be modified to trigger the blinker module reset at the start of the simulation. But that's a lot of work. A simpler solution, but not recommended in general, is to initialize the counter register value when it is declared. To do this, double-click the blinker module in the Hierarchy pane of the Navigator window. This will open the blinker module. Then change the cnt\_r declaration on line 39 to:

signal cnt r : std logic vector(22 downto 0) := (others=>'0');

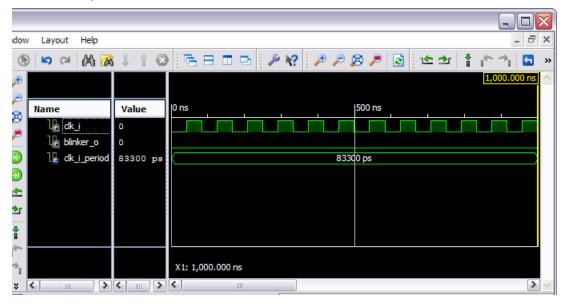

This will initialize all the counter register bits to zero. Save the blinker.vhd file. Then rerun the simulation by clicking on the **Simulation**  $\Rightarrow$  **Relaunch** menu item. Now the blinker o output takes on a value of zero at the start of the simulation.

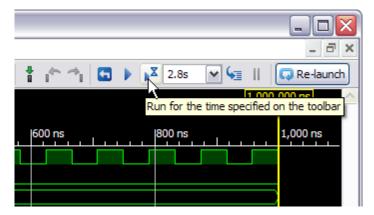

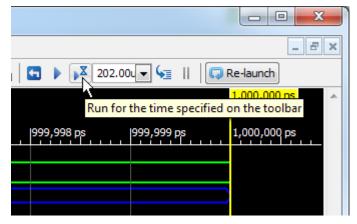

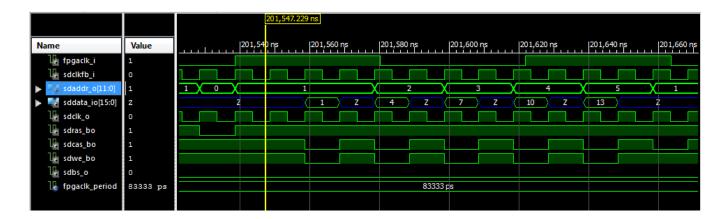

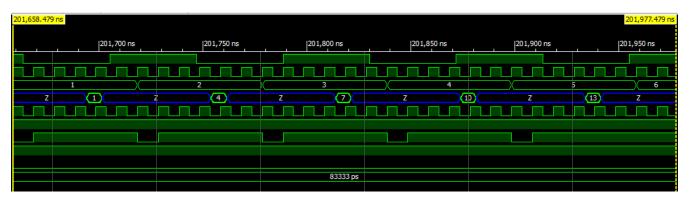

But you still don't know if the blinker output is going to do anything (except sit at zero) because the simulation duration is too small. The blinker output should pulse every 0.7 s, so a simulation time of 2.8 s will be enough to see four pulses. Enter "2.8s" into the simulation run-time field on the ISim toolbar and then click on the Run button.

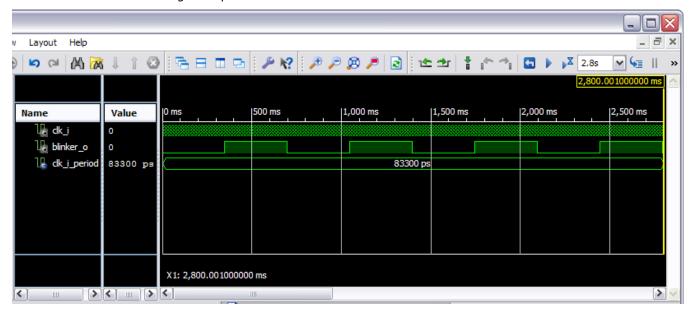

After a minute or two (because computing 2.8 s of simulation time takes a lot of work), the results of the simulation will appear. Use the **View**  $\Rightarrow$  **Zoom**  $\Rightarrow$  **To Full View** menu item to display the entire simulation. You can see that the blinker\_o output pulses four times during the 2.8 s simulation, giving a period of 0.7 s. So the blinker seems to be working as expected.

This chapter has been all software. Even the blinker, when it runs, is executing in software. That's not the reason you're interested in FPGAs, is it? No! - you want to build circuits that run in the real world. And that's what you'll do in the next chapter.

# C.4 "I have a netlist. Now what?"

# Physical Hardware - the XuLA Board

OK, you've designed the blinker in VHDL. You've synthesized it. You've simulated it and it seems to work. But, up to now, it's all been *virtual*. Now it's time to get *physical*.

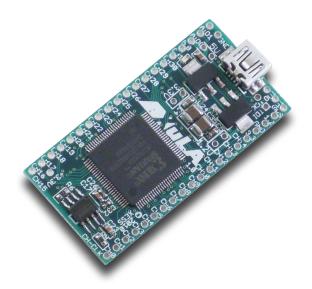

To get the blinker design into the real world, you'll need an FPGA chip. But the FPGA chip isn't much good by itself because its usually in a surface-mount package that can't be plugged directly into a breadboard. And it needs some type of interface to download the bitstream from the host (where WebPACK is running). And it would be nice to have some ancillary circuitry around the FPGA for providing clock signals, etc. For these reasons, you'll probably need an *FPGA development board*. For this book, I've chosen the <u>XuLA board</u>, but you can use other boards for the same purpose.

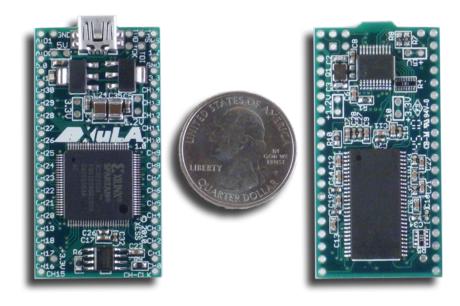

Here's a picture of the front and back of the XuLA board. The FPGA is the big chip on the front below the "XuLA" logo. (No, it is *not* the quarter.)

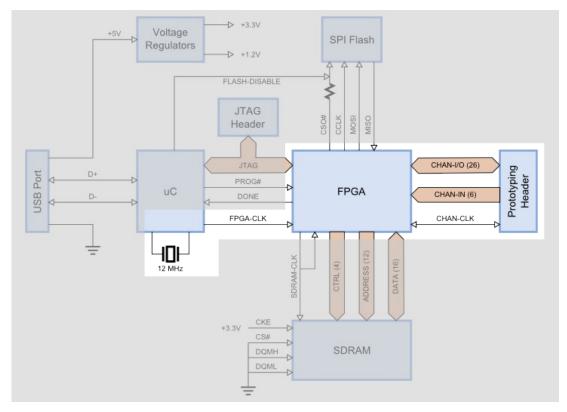

Here's a block diagram of what's on the XuLA board. You can safely ignore the most of the board's circuitry for now. I've highlighted the following parts that will be important for the blinker design:

**FPGA**: Of course the FPGA is important! I shouldn't need to explain why that is at this point. The FPGA is the Xilinx XC3S200A in a 100-pin QFP package (xc3s200a-4vq100), just like the one you selected when you started the blinker project in the last chapter.

**Clock input**: The XuLA board provides a 12 MHz square-wave clock to the FPGA. That will be the clock you'll use as the input to the blinker design.

**Prototyping header**: Some pins on the FPGA chip are connected to header pins around the outside of the XuLA board. These header pins are a convenient way to access signals from the FPGA when the XuLA board is inserted into a standard breadboard. You'll output the blinker\_o signal on one of the FPGA pins that goes to this header and connect an external LED to it.

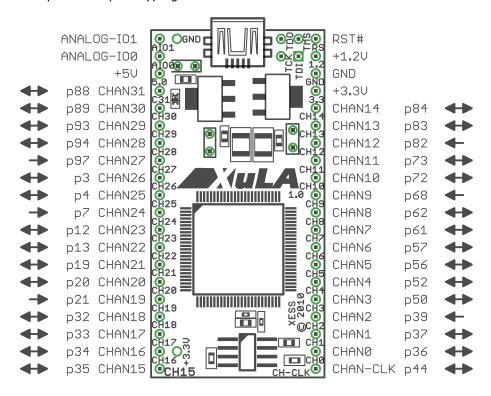

Finally, here's how the pins of the FPGA are assigned to the XuLA prototyping header. The FPGA pin numbers begin with a "p" so, for example, pin p50 of the FPGA is connected to the CHAN3 pin of the prototyping header.

# Assigning I/O Signals to FPGA Pins

Now that you know a little bit about the hardware that will be running your blinker design, you can proceed to the implementation phase. Open the ISE Project Navigator and return to the blinker project. Then move your project from simulation mode to implementation mode by clicking on the **Implementation** button in the **Views** pane.

Before you can pass the synthesized netlist through the implementation tools, you'll need to tell them what pins of the FPGA will be used for the input and output ports of your blinker. Otherwise, the tools will just assign them to any pins it deems fit for the purpose. An *Implementation Constraints File* (sometimes called a *User Constraints File* or UCF) is used to assign I/O signals to the FPGA pins.

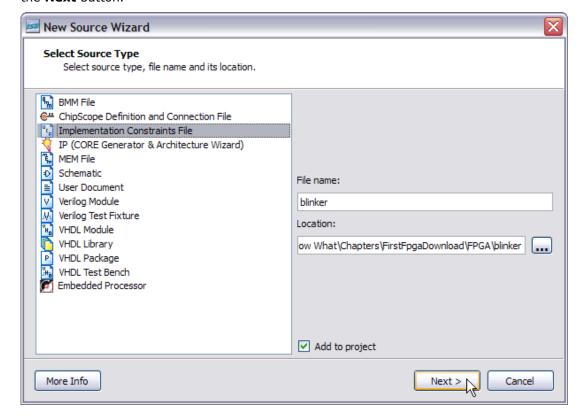

To add a constraints file to your project, right-click in the **Hierarchy** pane and select **New Source...** from the pop-up menu. In the New Source Wizard window, select **Implementation Constraints File** as the source type and give it the name "blinker". (You don't have to give it the same name as the project, but I usually do.) Then click on the **Next** button.

Another summary window will appear. Ho hum. Click on the **Finish** button and your constraints file will appear in the Hierarchy pane. Double-click on the constraints file and it will open in the workspace area to the right.

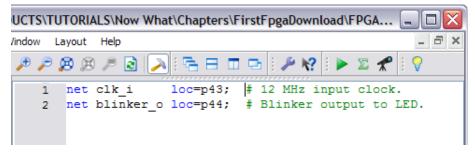

Type the following two lines into the blinker.ucf file and then save the file.

The first line assigns the  $clk_i$  net to pin location p43 of the FPGA. This is the pin that is driven by the 12 MHz clock on the XuLA board. (I know because I read the XuLA manual.) The implementation tools will look through the blinker netlist and see that  $clk_i$  is an input net, and then they will configure the IOB for p43 as an input buffer.

Similarly, the second line assigns output net blinker\_o to pin location p44 whose IOB is then configured as an output driver. Why p44? Because that is one of the FPGA pins connected to the XuLA prototyping header. Pin p44 exits the XuLA board on the lower-right corner pin labeled "CHAN-CLK".

That's all you need to do before running the implementation tools.

## **Doing the Implementation**

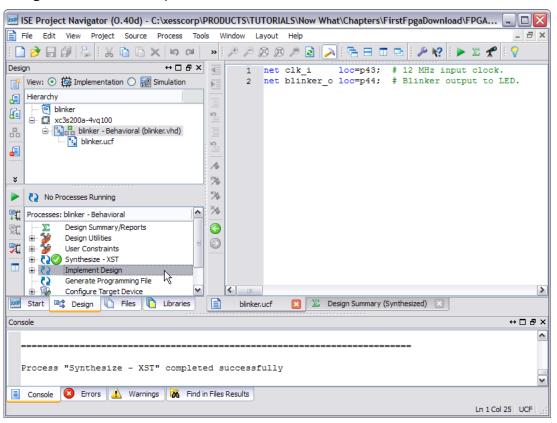

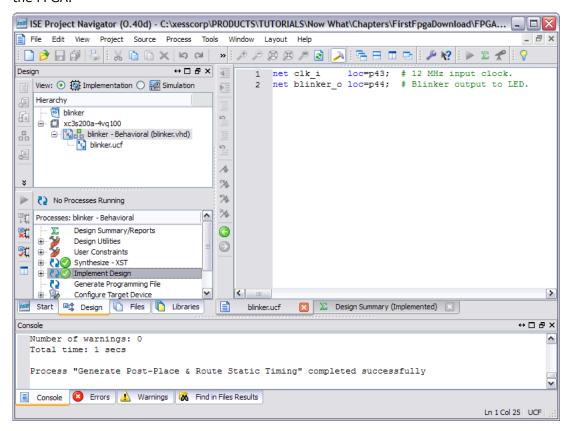

After all this work, the actual implementation is going to be rather anticlimactic. To begin, highlight the blinker module in the **Hierarchy** pane. Then, double-click **Implement Design** in the **Processes** pane.

You'll see messages scrolling through the **Console** tab in the **Transcript** window. In less than a minute (depending upon the speed of your PC), the translation, mapping and place & route phases will be done and a green check-mark will appear. You have successfully implemented your blinker! Now you have to get it into a form that you can download into the FPGA.

# **Preparing the Bitstream**

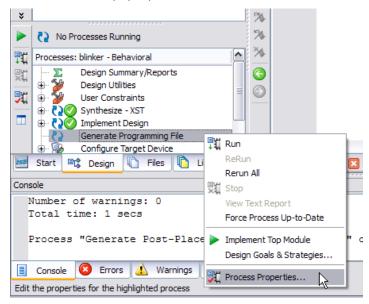

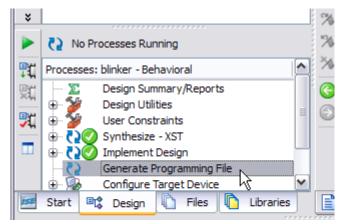

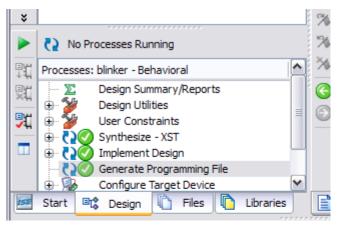

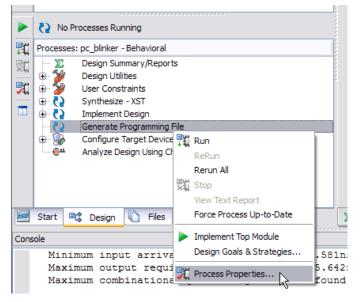

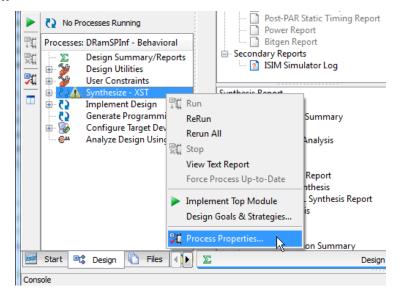

To generate the bitstream, all you have to do is double-click **Generate Programming File** in the Processes pane. *But don't do that yet!*

First, you have to change some configuration settings to make the bitstream compatible with the XuLA board. To do this, right-click on **Generate Programming File** and select **Process Properties...** from the pop-up menu.

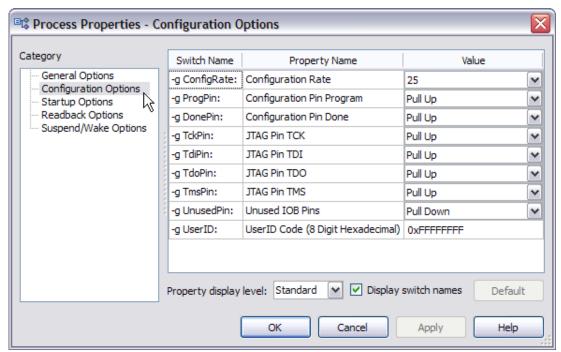

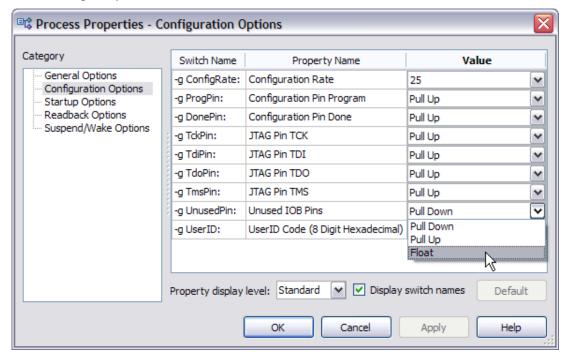

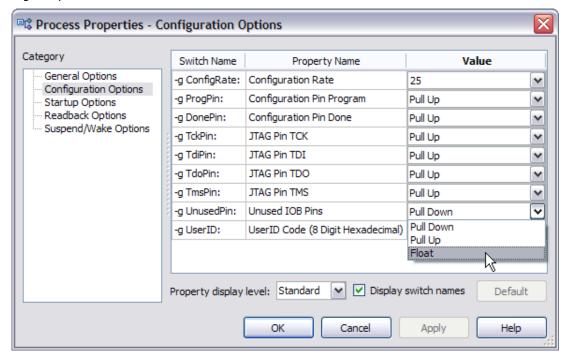

In the **Process Properties** window that appears, click on the **Configuration Options** category.

Then, click on the **Unused IOB Pins** drop-down menu and select **Float** from the list of options. This will cause all FPGA I/O pins that are not specifically used in your design to float in a high-impedance state.

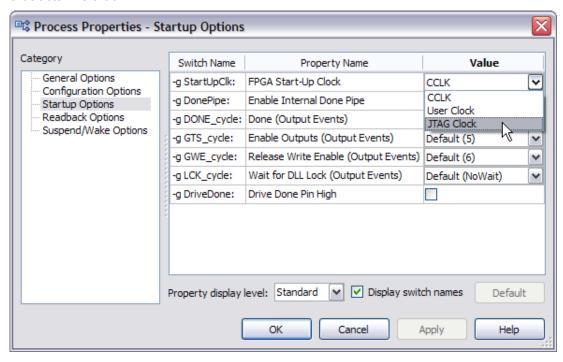

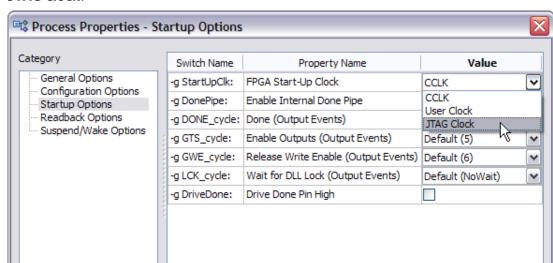

Now click on the **Startup Options** category and change the **FPGA Start-Up Clock** to **JTAG clock**. The FPGA on the XuLA board is programmed through the JTAG port and the clock that kickstarts your design right after downloading also comes through there. If you select any other option, your design will just sit in the FPGA and not do anything because it hasn't gotten a startup clock. This is always a good thing to check if you have a design that acts like that.

After setting these two options, click on the **OK** button and return to Navigator. Now you can double-click **Generate Programming File** to build the bitstream for the blinker project.

If the bitstream is generated successfully, you should be rewarded with the sight of three green check-marks!

Now that you have the blinker project bitstream, we will leave Navigator and use a XuLA-specific tool to download the bitstream.

# **Installing the XSTOOLs Utilities**

To download bitstreams to the XuLA board, you'll need to install the XSTOOLs utilities. You can download them <a href="here">here</a>. After you download the installer, just double-click it and accept the default installation settings. You'll download the blinker bitstream to the XuLA board using the GXSLOAD utility that gets installed.

# **Connecting the XuLA Board**

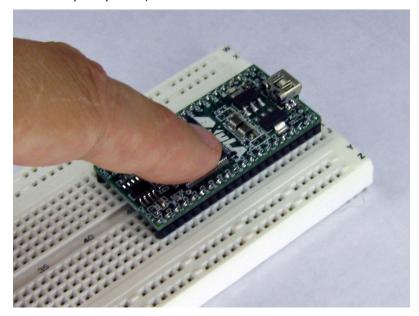

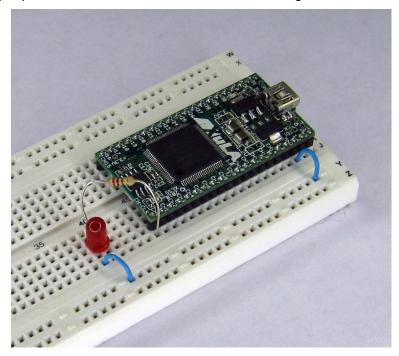

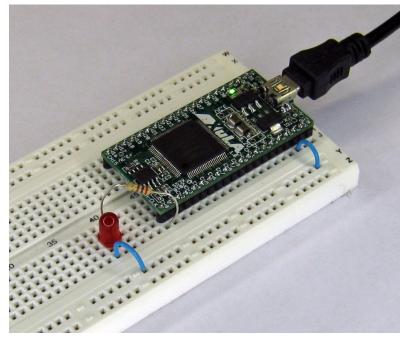

Before you download the bitstream, you'll need to hook a resistor and LED to the XuLA Board. This is relatively easy. First, insert a XuLA board into a breadboard.

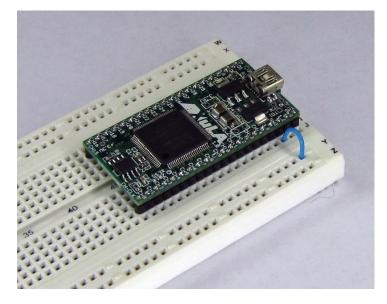

Then connect the ground connection of the XuLA board to the ground bus of the breadboard.

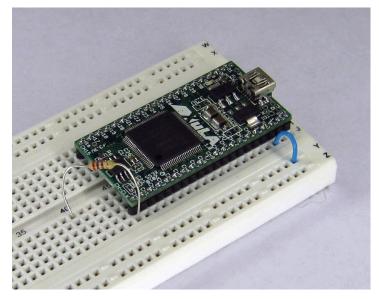

Add a resistor from the prototyping header pin that carries the blinker\_o signal. (The resistor value can be anywhere in the range of  $100\Omega$  to  $500\Omega$ .)

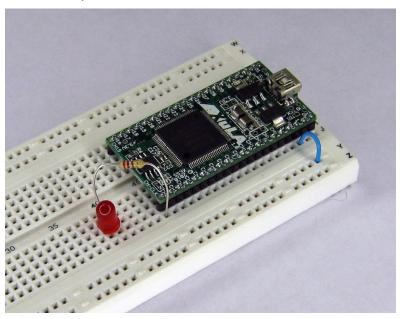

Insert an LED with the anode (the rounded side of the case) connected to the resistor and the cathode (the flat side of the case) plugged into an empty breadboard row. (I apologize – the leads on my diode were too short and you can't actually see where they plug into the breadboard.)

Then use a jumper wire to connect the LED's cathode to the ground bus.

Finally, connect a mini-USB cable from the XuLA board to the PC that you installed the XSTOOLs utilities on.

That's it! Time to dance.

# **Downloading the Blinker Bitstream**

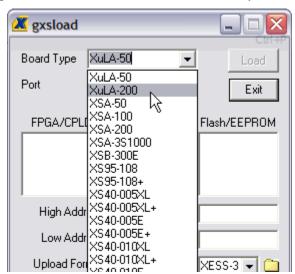

To begin the downloading process, double-click the GXSLOAD icon. This will bring up the following window:

Select the **Board Type** using the drop-down list. Since the blinker project was targeted at the XC3S200A, then you must be using a XuLA-200 board. (If you were using a XuLA-50 board, then your target FPGA would have been the XC3S50A.)

As for the **Port**, it should be set to **USBO** (if you only have one XuLA board connected to the PC).

Next, open the folder where you stored your blinker project. Locate the blinker.bit bitstream file and drag-and-drop it into the **FPGA/CPLD** pane of the **gxsload** window.

Once the bitstream file is dropped into the **FPGA/CPLD** pane, the **Load** button becomes active (i.e., it's no longer grayed-out). Just click on the **Load** button and the blinker bitstream will download from the PC into the FPGA on the XuLA board.

When the download begins, the green LED on the XuLA board will flash as the bitstream enters the FPGA. This LED will stop flashing once the complete bitstream has entered the FPGA. Then the blinker circuit will take control of the FPGA and it will start to blink the other LED you inserted into the breadboard. This <u>video</u> shows the downloading and operation of the blinker. If you time the flashing of the LED, you'll see it is pulsing once every 0.7 s as we hoped.

This completes your first design. You coded it, synthesized it, simulated it, implemented it, generated it, built it, downloaded it and ran it. You are officially an FPGA designer. A beginner, true, but an FPGA designer none the less.

# C.5 "Only 12 MHz! Now what?"

# **Speed Envy**

In the last chapter, some of you were probably saying: "A 12 MHz clock? That's all!? My Arduino runs faster than that. My *grandmother* runs faster than that!" (Maybe your grandmother, but not mine, both of whom died long ago. If you see them up and running around, then something's *really* gone wrong.)

One of the unfortunate consequences of the popularization of computers has been people's fixation on clock speed, with more being better. But fear not that your Arduinototing compatriots will laugh at you, because the FPGA on the XuLA board has a feature that will let it run at over 300 MHz.

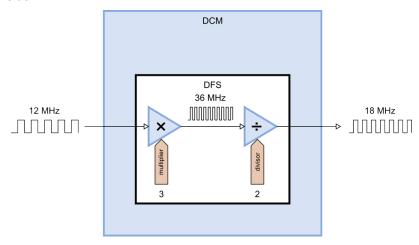

# The Digital Clock Manager

Modern Xilinx FPGAs contain *Digital Clock Managers* (or DCMs) that serve many functions, one of which is multiplying the frequency of a clock. A *Digital Frequency Synthesizer* (DFS) within the DCM can multiply an incoming clock signal by any integer in the range 2..32 and then divide it by any factor in the range 1..32. Here's an example of generating an 18 MHz clock:

With a 12 MHz input clock and a multiplier of 32, you can theoretically generate a clock up to 384 MHz, but the <u>practical electrical limit for a Spartan-3A device</u> is between 320 to 350 MHz (depending upon the speed grade of the FPGA).

# Adding a DFS to the Blinker

Now, how am I going to demonstrate the operation of a DFS to you if you don't have an oscilloscope to view the incoming and outgoing clock signals? Simple! We can take the blinker design from the previous chapter, add a DFS to multiply the input clock, and then see if the blinker pulses faster.

So the first thing to do is to add the DFS to the blinker VHDL file. But how do you describe a DFS in VHDL? After all, it's not something simple like a NAND gate or a counter.

Well, Xilinx has made it easy for you by creating a *device primitive* for the DFS. (It's called a primitive because it can't be decomposed into a collection of simpler components. Perhaps *atom* would have been a better name.) You can instantiate the DFS device primitive into your VHDL source and not have to worry about how it is actually built.

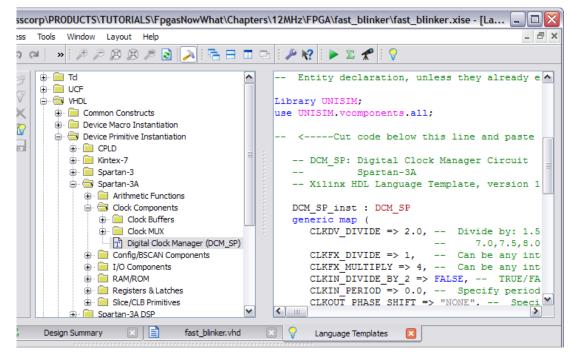

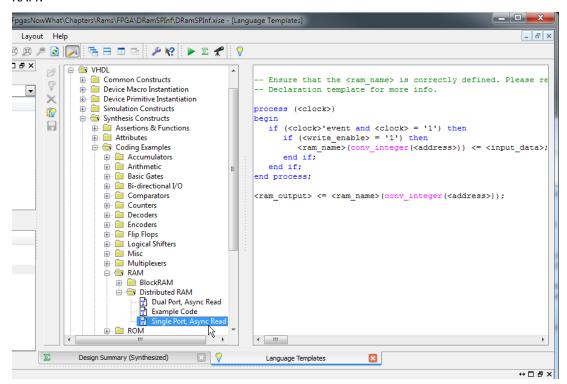

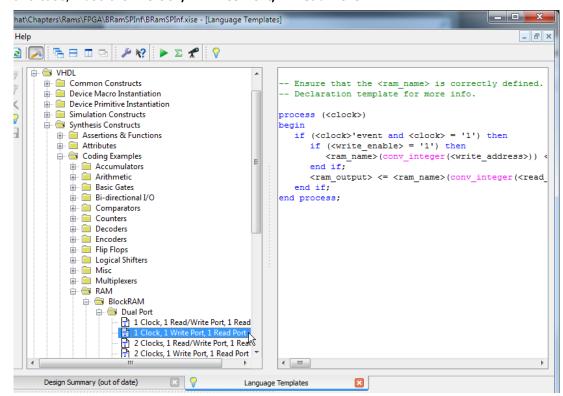

But you need to know what the inputs and outputs of the DFS primitive are in order to use it. To get this information, click on the **Edit**  $\Rightarrow$  **Language Templates...** menu item. This will make the Language Templates tab appear in the workspace pane like so:

To find the DFS primitive, click on the **VHDL** folder and expand it until you see the DCM item appear. Then select the DCM item and a VHDL template for instantiating this primitive will appear in the rightmost pane.

The VHDL template is intimidating! There are eighteen inputs and outputs and twelve generic parameters for tuning the operation of the DCM primitive. But we can ignore most of them and accept their default settings. The only things we care about for this application are the reset (RST), input clock ( $CLK_IN$ ), the DFS output clock ( $CLK_FX$ ), and the DFS multiplier (CLKFX MULTIPLY) and divider (CLKFX DIVIDE).

After instantiating the DCM and doing some trimming and editing, the blinker VHDL looks like what's shown on the following page. Here's what changed:

**Lines 26-27:** Since the DCM primitive is being used, these lines need to be uncommented to bring in the Xilinx primitive libraries.

**Line 35**: A new signal, clk fast, was added to carry the clock generated by the DFS.

Lines 39-48: The DCM is instantiated here. The DFS divider and multiplier are set to one and four, respectively, on lines 41 and 42. The DFS output is connected to the clk\_fast signal on line 45, and the input clock is connected to the DFS clock input on line 46. The reset input is tied to an inactive level on line 47.

Lines 50-55: The clock for the counter was changed from clk in to clk fast.

```

20

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

21

use IEEE.STD_LOGIC_UNSIGNED.ALL;

22

23

-- Uncomment the following library declaration if instantiating

24

-- any Xilinx primitives in this code.

25

library UNISIM;

26

27

use UNISIM.VComponents.all;

28

29

entity fast blinker is

30

Port ( clk_i : in STD_LOGIC;

blinker_o : out STD_LOGIC);

31

32

end fast blinker;

33

architecture Behavioral of fast_blinker is

34

35

signal clk fast : std logic;

signal cnt_r : std_logic_vector(22 downto 0) := (others=>'0');

36

37

begin

38

DCM SP inst : DCM SP

39

generic map (

40

41

CLKFX DIVIDE

=> 1, -- Can be any interger from 1 to 32

CLKFX MULTIPLY => 4 -- Can be any integer from 1 to 32

42

43

44

port map (

CLKFX => clk fast, -- DCM CLK synthesis out (M/D)

45

CLKIN => clk_i,

-- Clock input (from IBUFG, BUFG or DCM)

46

RST => '0'

-- No reset

47

48

);

49

process(clk fast) is

50

51

52

if rising_edge(clk_fast) then

53

cnt r <= cnt r + 1;

end if:

54

55

end process;

56

blinker o <= cnt r(22);

57

58

end Behavioral;

```

After the VHDL file is finished, you can run the synthesizer to see if there are any problems. (There aren't, at least when I did it).

# **Does It Work?**

That's always the question, especially when you are applying a chip feature that you haven't used before. So let's run a simulation to find out. First, add a new test bench to your project:

Then go into the test bench VHDL file and change the clock period to match the 12 MHz clock period:

```

55

56 -- Clock period definitions

57 constant clk_i_period : time := 83.3 ns;

58

```

Then switch to the **Simulation** view of your project and click on the **Simulate Behavioral Model** item in the **Processes** pane. When the **ISim** window appears, enter 2.8s in the simulation duration field and then click on the run button.

Then be prepared to wait ... for ... a ... very ... long ... time. On my PC the simulation took about 30 minutes, probably because simulating the DFS is computationally demanding. After the simulation finishes, compress the view so the entire 2.8 s time interval is visible and count the number of blinker pulses. You should see sixteen pulses. Remember in the previous blinker design, there were only four pulses in the 2.8 s window. So it appears – at least in the simulation – that the DFS has multiplied the 12 MHz clock by a factor of four.

# **But Does It Really Work?**

That's always the *real* question: Will it work in the FPGA? Well, it's easy enough to find out. Here are the high points for how to do that:

- 1. Connect an LED and resistor to the XuLA board just as you did for the previous blinker project. Then connect the XuLA board to a USB port on your PC.

- 2. Add a constraints file to your project that's identical to the one you used for the

- previous blinker project since the LED and clock pin assignments haven't changed.

- 3. Right-click the **Generate Programming File** process item and select **Process Properties...** from the pop-up menu. Then select the options to float any unused I/O pins after configuration and to use the JTAG clock as the start-up clock.

- 4. Double-click the **Generate Programming File** process. This will run the synthesis and implementation tools in sequence and then create a downloadable bitstream.

- 5. Start the GXSLOAD tool and drag-and-drop the fast\_blinker.bit file into the **FPGA** pane. Then click the **Load** button to download the bitstream into the FPGA on the XuLA board.

After doing these steps, you should be rewarded by seeing the LED attached to the XuLA board blinking away at about six times per second.

# C.6 "No LEDs! No buttons! Now what?"

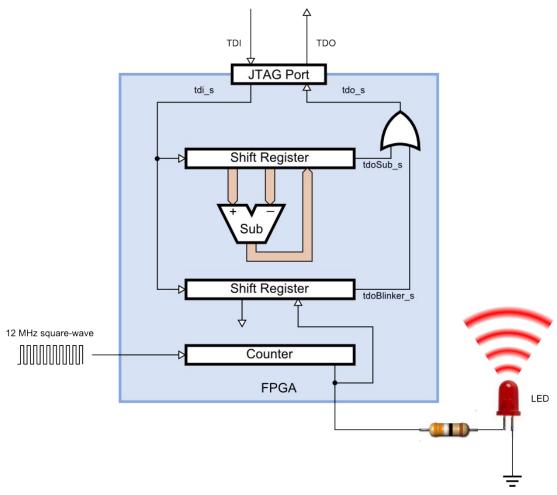

# **Blinky Envy**

By now you're probably saying to yourself: "Trying to tell what my design is doing by looking at a flashing LED really sucks! All the other FPGA boards have loads of flashing LEDs. And they have bunches of buttons and switches! My XuLA board has *nothing*!"

Now when you learned how to ride a bike, you might have started out using training wheels. These were helpful – they let you get experience with the bike without getting hurt (unless your parents *push you out in a busy street* – but that's another story). But after a while, you couldn't wait to get rid of those training wheels. Wherever you went, they just screamed out: "I'm a bike-riding noob! Come give me a wedgie!" But the worst part is they got in the way; you couldn't get any speed up because those training wheels were dragging on the ground. Luckily, they weren't welded to the bike and you could take them off. Then you could use the bike for what it was for: getting you from here to there faster and easier than being on foot.

LEDs and buttons are similar to training wheels: good when getting started, but a hindrance after that. LEDs and buttons are meant to operate at human interaction speeds, like 10 Hz or less. But FPGAs are meant for applications that run at hundreds of MHz; it's a waste to have them waiting around while you look at an LED and then push a button to tell them what to do! Plus, they're hard to use for anything but the simplest designs: do you really want to flip switches to input a three-digit hexadecimal number and then translate the pattern on a bunch of LEDs back into hex? (If you do, then I've got a PDP-8 in the basement with your name on it!)

But LEDs and buttons are different from training wheels in one important aspect: they aren't easy to take off when you're done with them. They're usually soldered to the board where they take up space (and make the board larger than it needs to be). They interfere electrically when you use the FPGA pins for other purposes (unless there are jumpers to disconnect them, taking up even more space). And they're never connected to the pin you want them on (although this is less of a problem with FPGAs since you can move your I/O signals from pin to pin as you please).

Still, there is no denying that you need some way to observe what your design is doing. Logic probes are one solution (sort of a portable LED), but limited in the amount of information they can present (just like an LED). Oscilloscopes are good for capturing signal behavior, especially at high frequencies, but most scopes have four inputs or less

and they cost a fair bit of money (around \$300 for a minimal scope). Logic analyzers provide a lot of inputs that can be sampled at hundreds of MHz, but they are truly a pain to hook up to your circuit (but they are much cheaper now: as little as \$50). A companion to the logic analyzer is the digital pattern generator which can drive signals into your design and which suffers from the same connection difficulties as the analyzer.

The ideal solution for observing what your application circuit is doing would have these characteristics:

- Free.

- Flexible.

- Easy to use.

- Takes up no space.

- Uses no FPGA pins.

- Lets you drive inputs into your circuit and also observe its response.

- Drives inputs into your circuit and observes its response *automatically*.

- Goes away when you no longer need it.

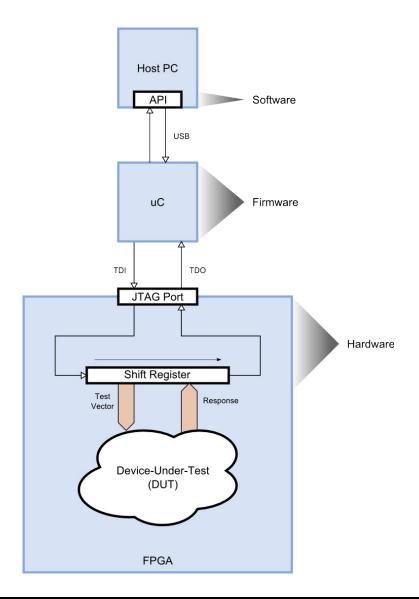

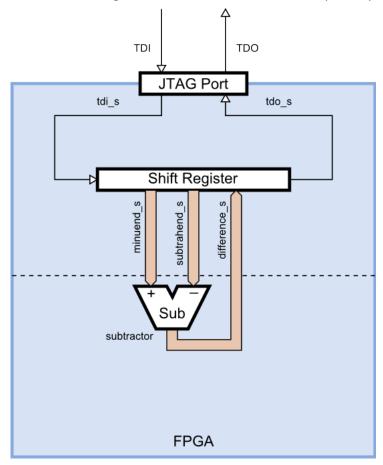

This sounds like a fantasy product, but you actually already have it! The FPGA itself can provide the circuitry you need to monitor and control your own application circuit. Here's the basic idea: shift a test vector into the FPGA, apply it in parallel to the inputs of your circuit, load the output response of your circuit into the shift register and shift it out of the FPGA (see the figure below).

You need three things to make this work:

- 1. Hardware modules are needed for the interface through the FPGA's JTAG port, the shift register, and other housekeeping details.

- 2. Firmware is needed for the microcontroller on the XuLA board so it can transfer the test vectors and responses between the FPGA's JTAG port and the USB port of a host PC.

- 3. Software is needed on the host PC to make it easy to generate, transmit, receive and display the test vectors and responses.

Now that's a lot of stuff to build and test, but luckily I've already done that for you. All you have to do is apply it to your own circuits. And I'll show you an example of how to do that using our old friend – you guessed it – the LED blinker!

# Monitoring the LED Blinker from the Host PC

#### **Modifying the LED Blinker Project**

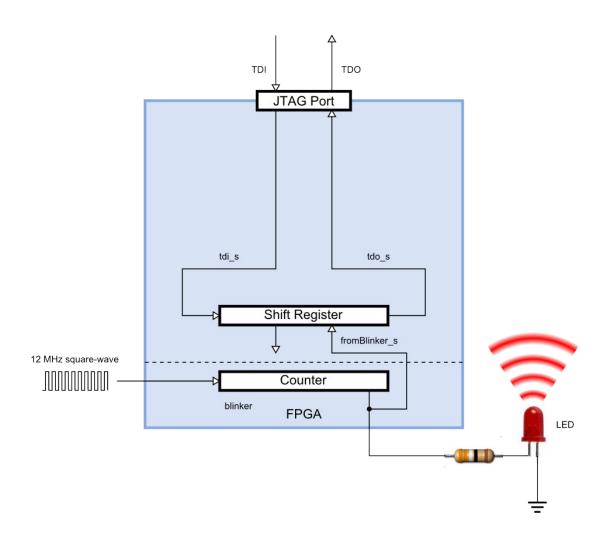

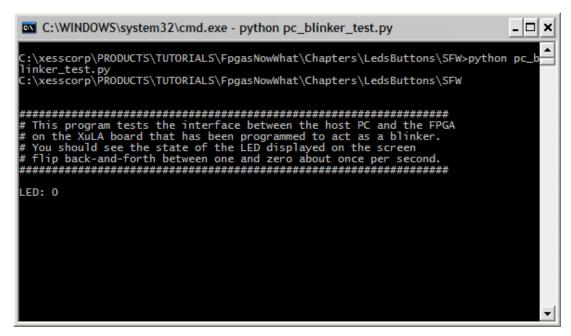

Before diving into the VHDL code, it might be helpful to get a picture of what we're trying to do. The original LED blinker circuit from Chapter 3 is shown at the bottom of the figure below: it takes a 12 MHz clock, divides the frequency down using a counter, and attaches one bit of the counter to an LED so it flashes about once per second. The counter bit is also loaded into a shift-register (although it's not *just* a shift-register) where its value can be shifted out of the FPGA through the JTAG port and on to a PC. The PC could also shift in bits to drive inputs to the counter, but the counter has no inputs so these signals are left dangling. There are a few other signals running around in the background that aren't shown so I don't complicate the very simple technique that is being used here. Don't worry, you'll be seeing them soon.

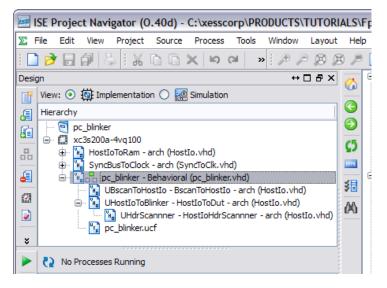

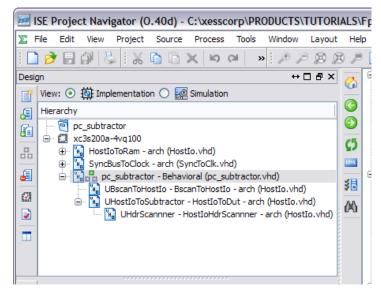

Now on to the VHDL. The list of files needed to add the JTAG interface and shift-register modules to the LED blinker project are shown below. Here's what each one does:

**HostIo.vhd**: This file contains the VHDL for the JTAG entry point and shift-register modules that will let the host PC talk to the blinker circuit in the FPGA.

**Common.vhd**: Some helpful VHDL functions that are used in the HostIo.vhd code are defined in this file.

**SyncToClk.vhd**: This file describes some synchronization circuitry that is used in the HostIo.vhd file, but which has no role to play in this example. You need it to keep the VHDL synthesizer from complaining about undefined modules.

pc\_blinker.vhd: This is where the original LED blinker VHDL code is augmented with the modules found in HostIo.vhd.

**pc\_blinker.ucf**: The same pin assignments for the original LED blinker are repeated in this file.

The pc\_blinker module is where we want to concentrate our attention. Let's take a look inside:

The first three lines are the same as for the original LED blinker. They just import some standard packages from the IEEE library. But the fourth line is new: it imports the JTAG entry point and shift-register modules from the HostIo.vhd file. The work library just refers to the directory where the whole project is stored; <code>HostIoPckg</code> refers to the package of modules defined in the HostIo.vhd file; all just says to import every module found in the HostIoPckg (although I could have been more discriminating and just imported the modules that were needed by this design).

```

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.all;

3 use IEEE.STD_LOGIC_UNSIGNED.all;

4 use work.HostIoPckg.all; -- Package for PC <=> FPGA communications.

```

The next few lines declare the interface for the LED blinker. It is identical to the entity

declaration used in the original LED blinker. Even though we are going to monitor the LED blinker with the PC, the signals that pass in and out of the JTAG port do not need to be declared here.

```

6 entity pc_blinker is

7  port (clk_i : in std_logic;

8  blinker_o : out std_logic);

9 end entity;

10

```

The architecture section comes next. The 23-bit counter for the LED blinker is declared on line 12. Lines 14 and 15 declare two, 1-bit vectors: one for carrying bits from the PC to the blinker's inputs, and one to carry the outputs of the blinker back to the PC. (There are no inputs to the blinker, but a dummy signal is needed just to have something to connect to the shift-register module.) Even though these are both single-bit signals, they need to be declared as std\_logic\_vectors in order to match the declared I/O types of the modules in the HostIoPckq.

Lines 17-20 declare the signals that connect from the JTAG entry point to the shift-register. A selection signal and a clock are declared which are used to shift bits in and out of the register on the tdi\_s and tdo\_s signals.

```

architecture Behavioral of pc blinker is

11

signal cnt r : std logic vector(22 downto 0) := (others => '0');

-- Connections between the shift-register module and the blinker.

signal toBlinker s : std logic vector(0 downto 0); -- From PC to blnkr.

signal fromBlinker_s : std_logic vector(0 downto 0); -- From blnkr to PC.

1.5

-- Connections between JTAG entry point and the shift-register module.

16

17

signal inShiftDr_s : std_logic; -- True when bits shift btwn PC & FPGA.

signal drck_s : std_logic; -- Bit shift clock.

signal tdi_s : std_logic; -- Bits from host PC to the blinker.

signal tdo_s : std_logic; -- Bits from blinker to the host PC.

18

19

20

21

Begin

22

```

Next up is circuitry for the LED blinker. It's identical to what you've already seen in Chapter 3.

```

23

24

-- Application circuitry: the LED blinker.

25

26

2.7

-- This counter divides the input clock.

28

process(clk_i) is

29

begin

if rising_edge(clk_i) then

30

31

cnt r <= cnt r + 1;

32

end if;

33

end process;

34

3.5

blinker o \leftarrow cnt r(22); -- This counter bit blinks the LED.

36

```

The JTAG entry point module follows. The I/O for this module connects to the internal signals declared on lines 17-20.

```

37

______

38

-- JTAG entry point.

______

39

40

-- Main entry point for the JTAG signals between the PC and the FPGA.

41

UBscanToHostIo : BscanToHostIo

42

43

port map (

inShiftDr_o => inShiftDr_s,

44

45

drck o => drck s,

```

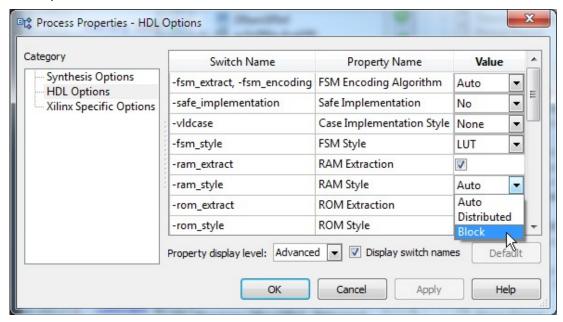

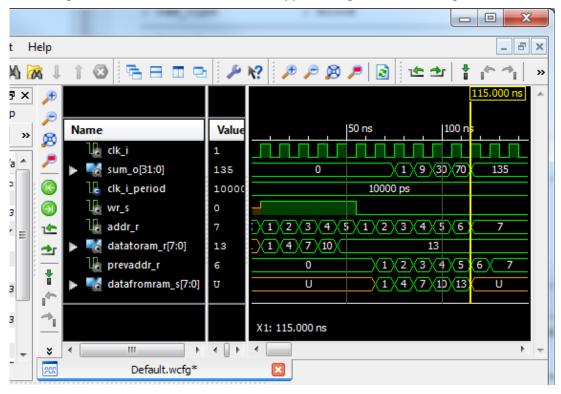

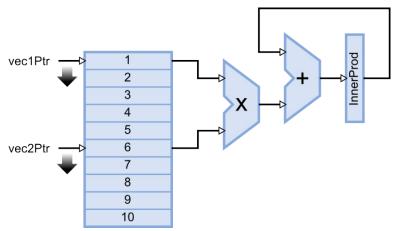

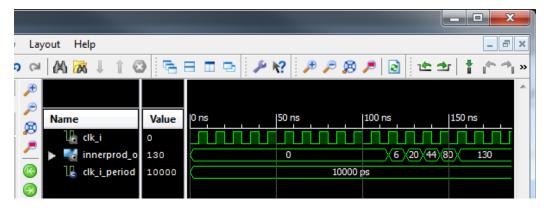

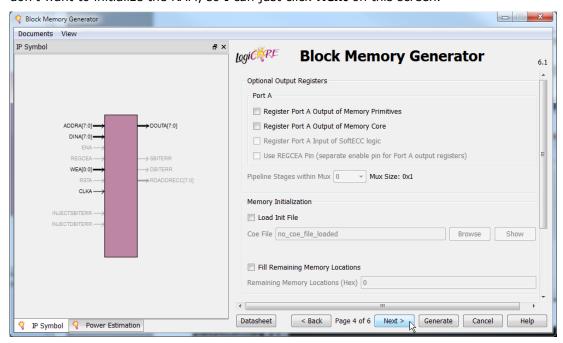

49