VERSION 2.0 Metalguy66/Warerat

## **Table of Contents**

|                                                                   | e of Contents      |     |

|-------------------------------------------------------------------|--------------------|-----|

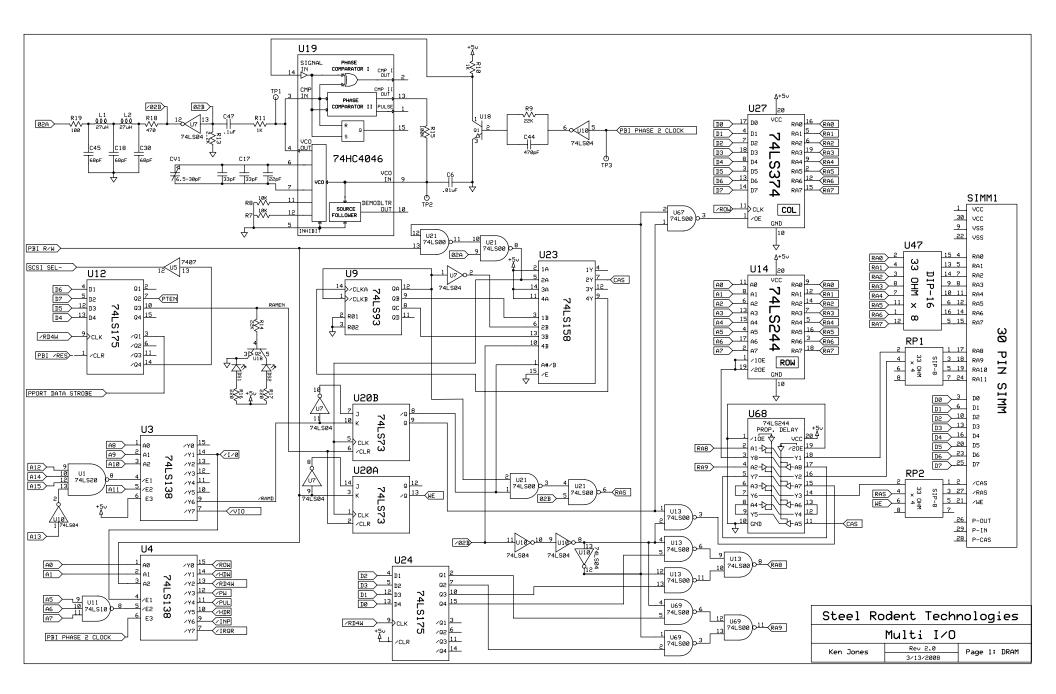

| Schematic Diagram                                                 |                    | 2   |

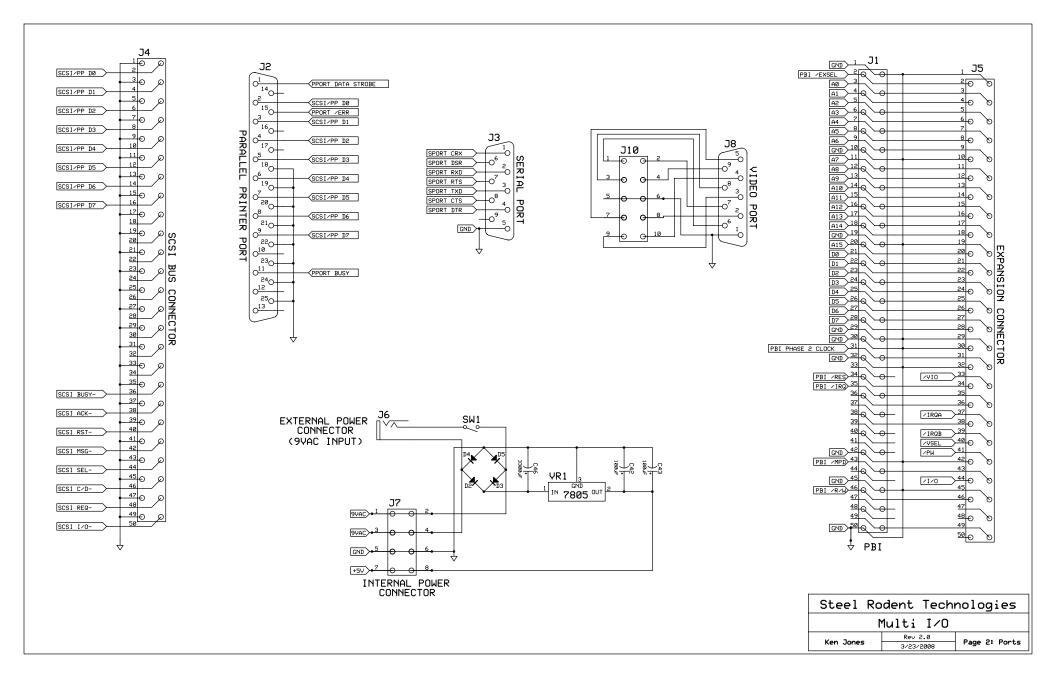

| DRAM Circuits Ports & Connectors                                  |                    | 2 3 |

|                                                                   |                    |     |

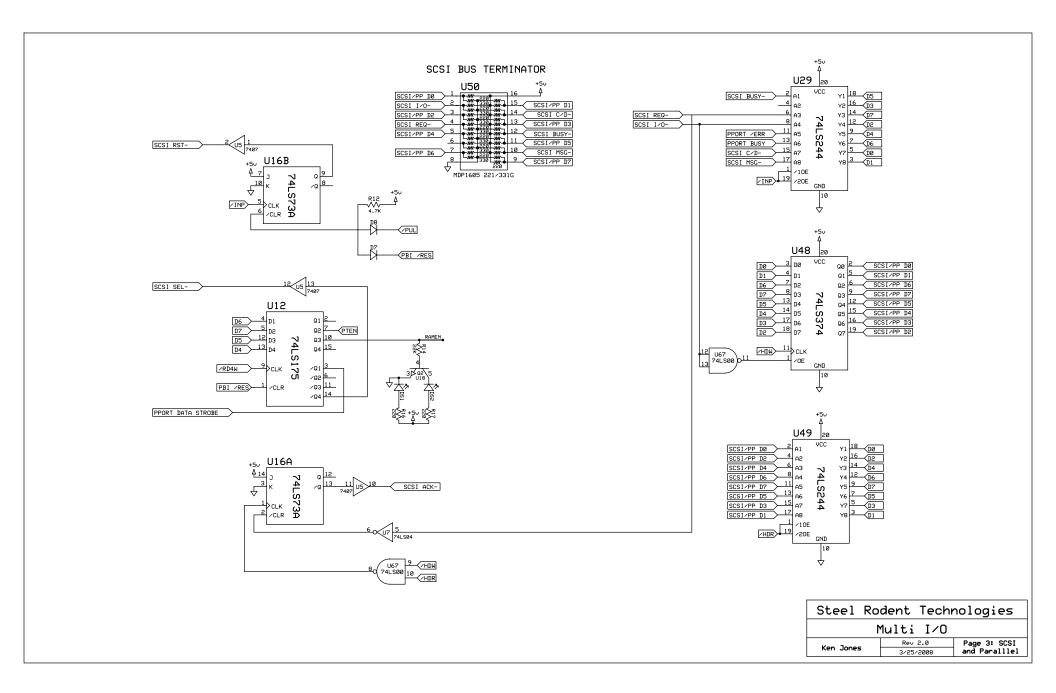

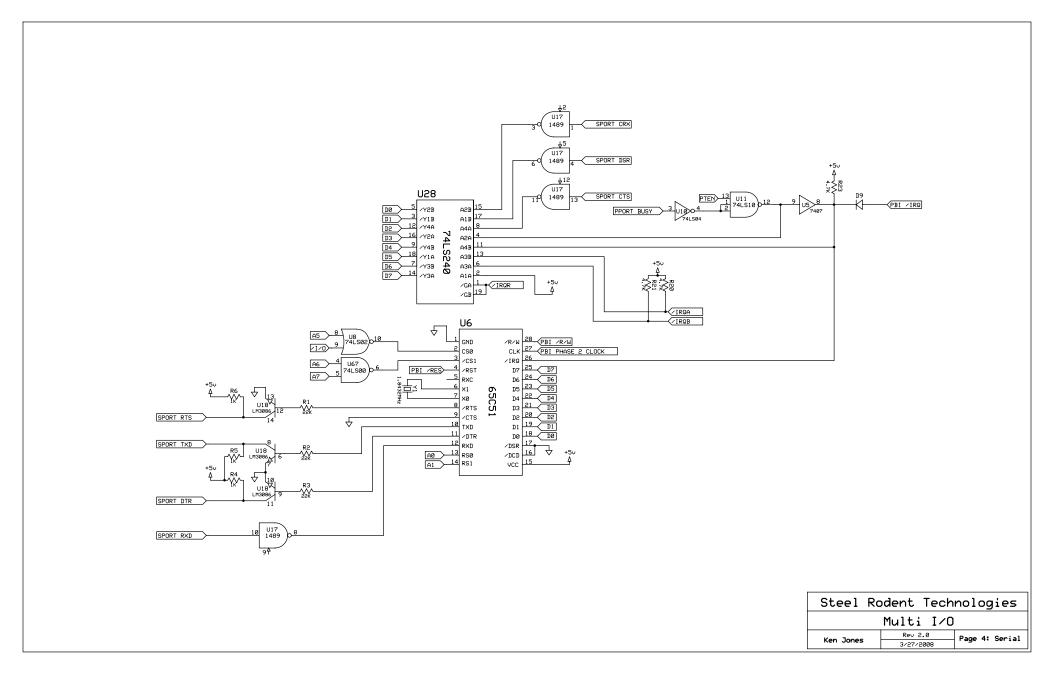

| SCSI and Parallel Interface Circuits<br>Serial Interface Circuits |                    | 4   |

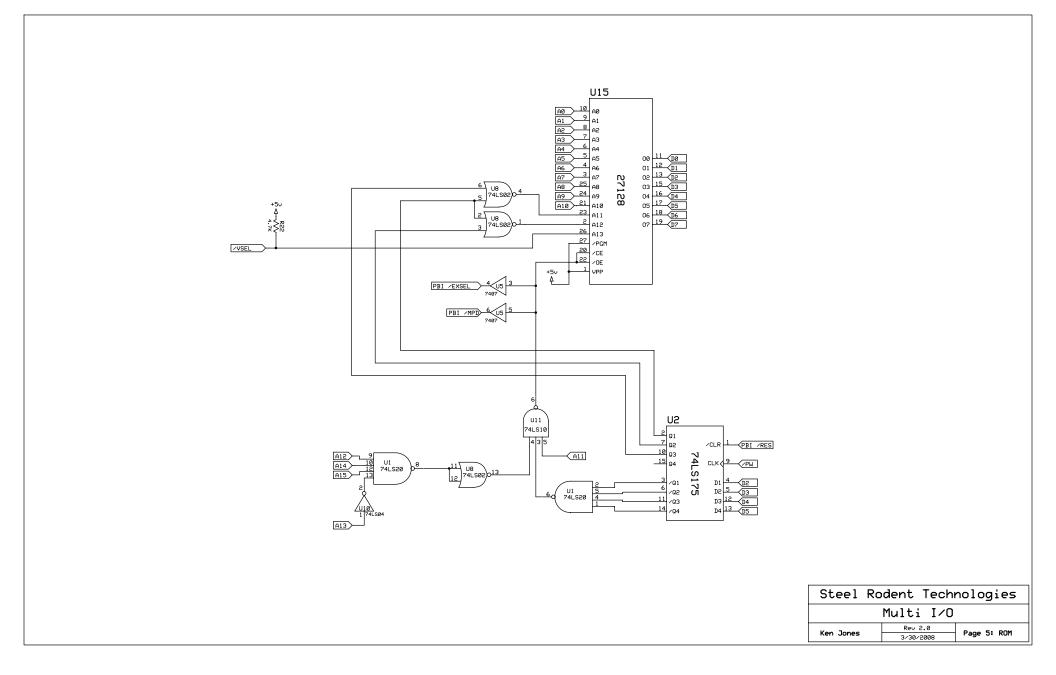

| ROM Circuits                                                      |                    | 5   |

|                                                                   |                    | 0   |

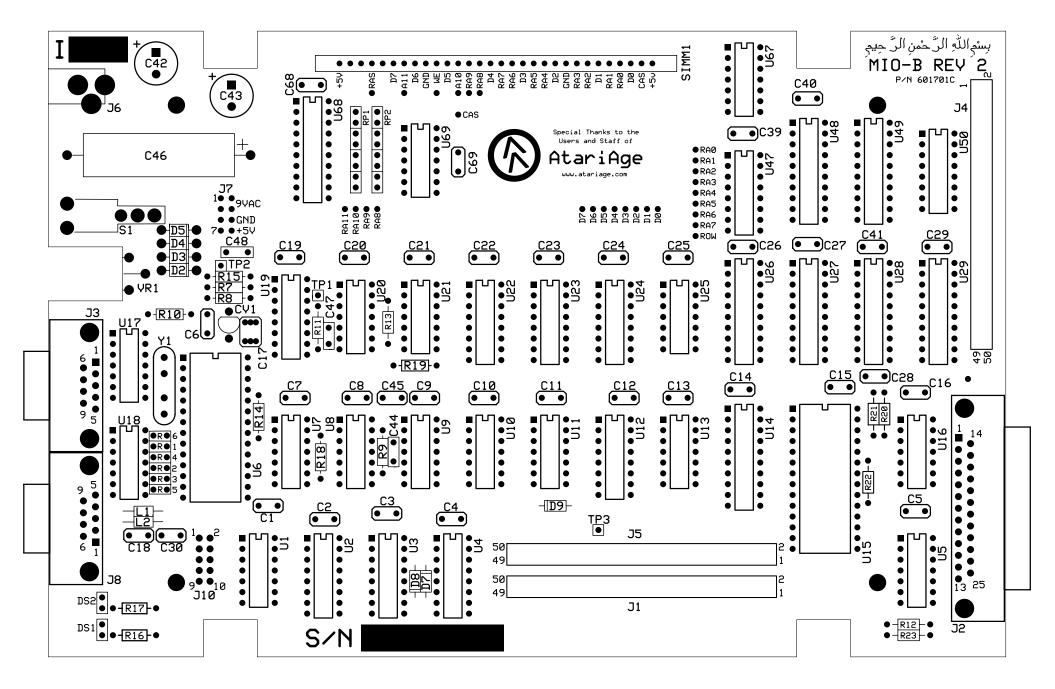

| Component Placement Diagram Parts List                            |                    | 8   |

| Integrated Circuit and Logic Data                                 |                    | 8   |

| U1                                                                | 74LS20             | 9   |

| U2, U12, U24                                                      | 74LS20<br>74LS175  |     |

| U3. U4                                                            | 74LS175<br>74LS138 | 10  |

| U5                                                                | 7407               |     |

| U6                                                                | 6551 ACIA          | 14  |

|                                                                   |                    |     |

| U7, U10                                                           | 74LS04             | 22  |

| U8                                                                | 74LS02             | 23  |

| U9, U25                                                           | 74LS93             | 24  |

| U11                                                               | 74LS10             | 27  |

| U13, U21, U67, U69                                                | 74LS00             | 28  |

| U14, U26, U29, U49, U68                                           | 74LS244            | 29  |

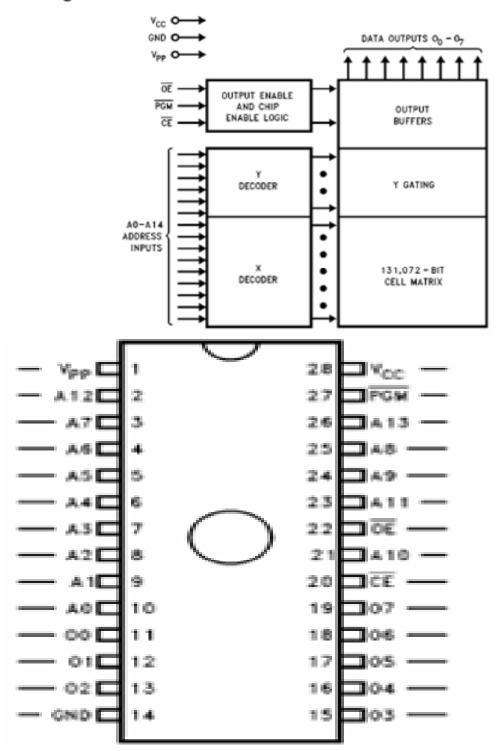

| U15                                                               | 27C128 EPROM       | 30  |

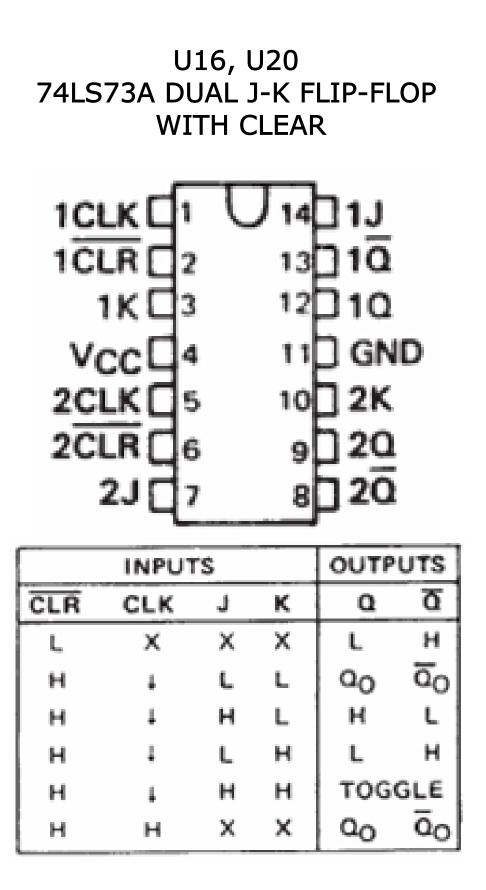

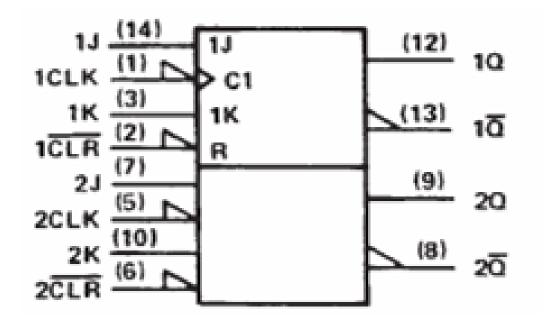

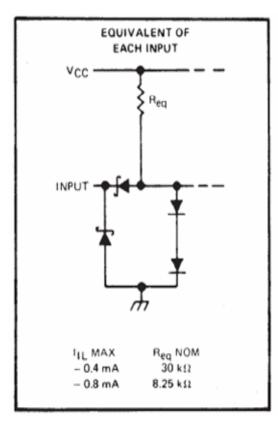

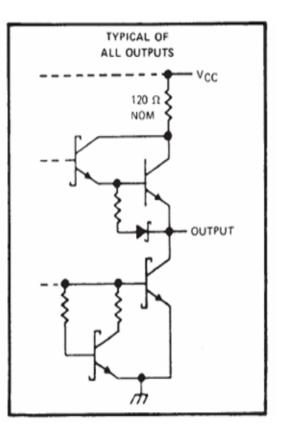

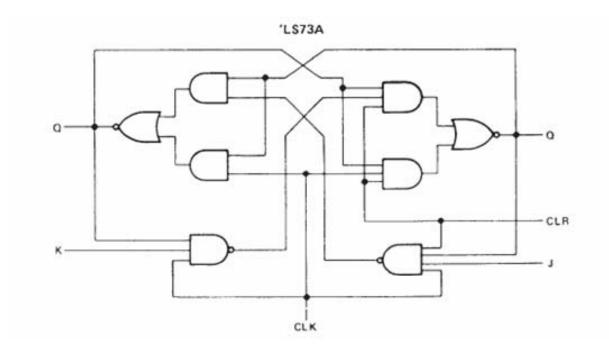

| U16, U20                                                          | 74LS73A            | 31  |

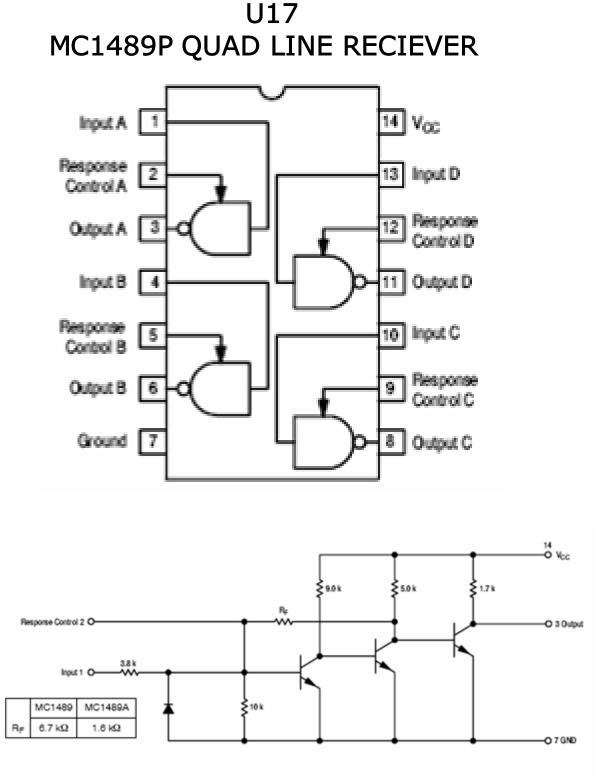

| U17                                                               | MC1489P            | 34  |

| U18                                                               | LM3086             | 35  |

| U19                                                               | 74HC4046           | 36  |

| U22                                                               | 74LS139            | 43  |

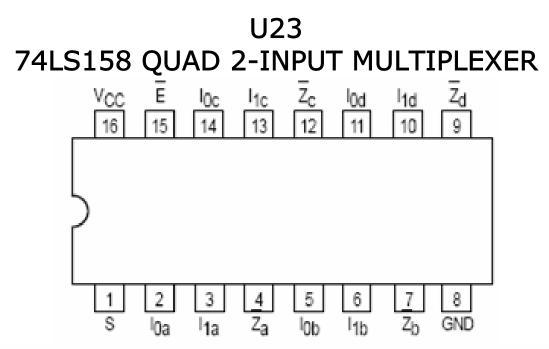

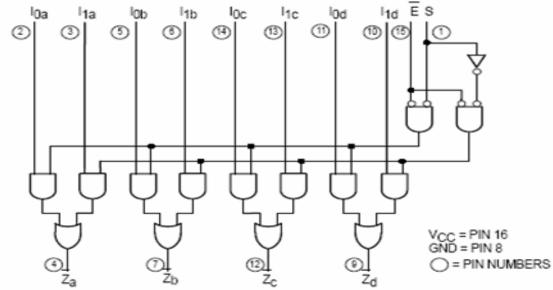

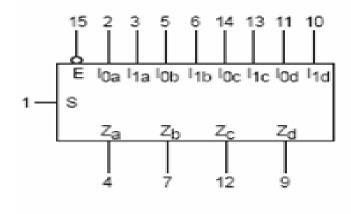

| U23                                                               | 74LS158            | 45  |

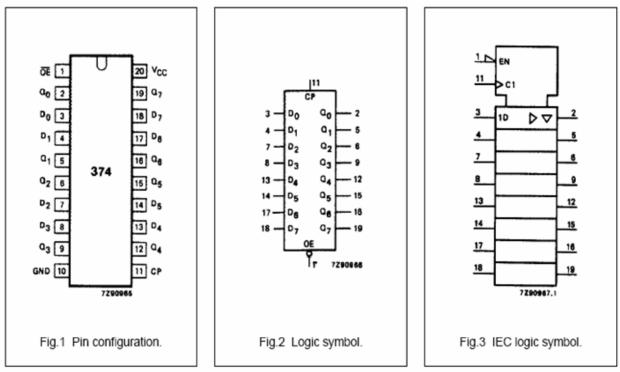

| U27, U48                                                          | 74LS374            | 47  |

| U28                                                               | 74LS240            | 49  |

| U47, U50                                                          | RESISTOR NETWORKS  | 50  |

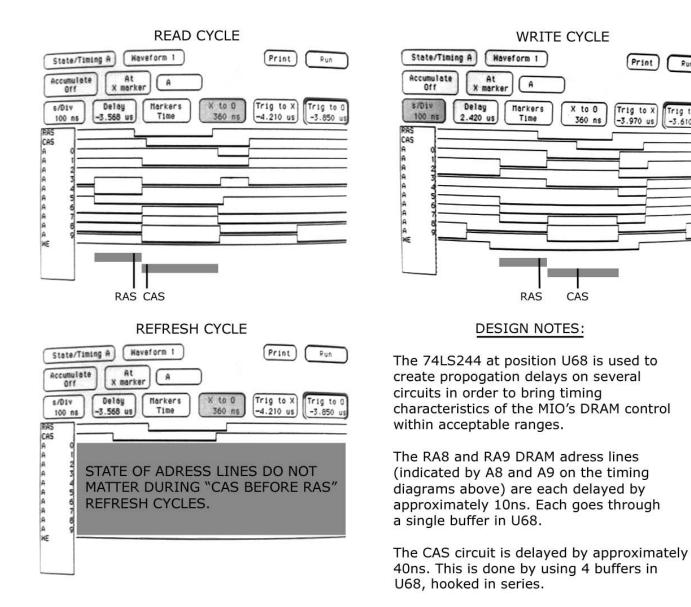

| DRAM Timing                                                       |                    | 53  |

| Theory: Signals                                                   |                    | 54  |

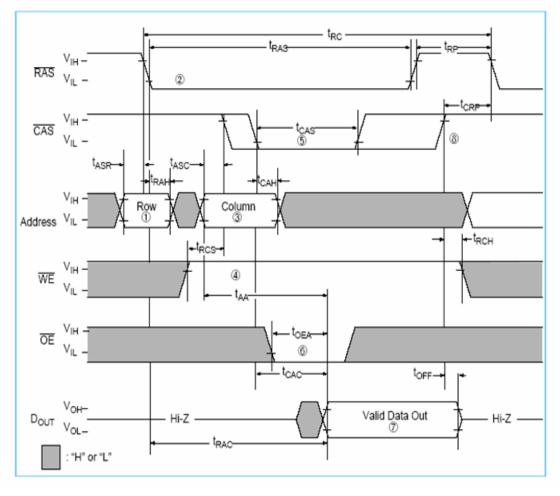

| Theory: Read Cycle                                                |                    | 55  |

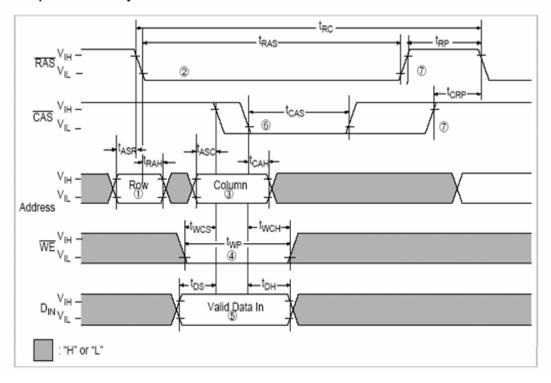

| Theory: Write Cycle                                               |                    | 56  |

| Theory: Refresh                                                   |                    | 57  |

| Programming Information                                           |                    | 58  |

| Hardware Description                                              |                    | 58  |

| Register Selection Table                                          |                    | 59  |

| ACIA Command Register                                             |                    | 60  |

| ACIA Control Register                                             |                    | 61  |

| RAM/ROM Access, IRQ Status                                        |                    | 62  |

| Software Description, Configuration Parameters                    |                    | 63  |

| Operating Variables                                               |                    | 64  |

| RS-232 Handler Functions and Tables                               |                    | 65  |

| Interface Standards                                               |                    | 70  |

| Standard Printer & MODEM Cables                                   |                    | 70  |

| Directly Compatible SCSI/SASI Devices                             |                    | 72  |

| Directly compatible Sebi/SNSI Devices                             |                    | 12  |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    | +   |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

|                                                                   |                    |     |

| Description                                                  | Value            | Qty per MIO | Layout number                             | Mouser number      | Digikey number      | cost                                                                                                                                         |

|--------------------------------------------------------------|------------------|-------------|-------------------------------------------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Transistor Array                                             | LM3086N          |             | U18                                       | 526-NTE912         |                     | \$5.18                                                                                                                                       |

| Quad Line Reciever                                           | MC1489P          |             | U17                                       | 511-MC1489P        |                     | \$0.28                                                                                                                                       |

| dual 4-input NAND gate                                       | 74HC20N          |             | U1                                        | 511-M74HC20        |                     | \$0.20                                                                                                                                       |

| Hex Inverter                                                 | 74LS04N          |             | U7,U10                                    | 311-M// 411020     | 296-1629-5-ND       | \$0.29                                                                                                                                       |

| 12v Phase locked loop (obsolete- very early MIOs only)       | MC14046          |             | U19                                       |                    | MC14046BCPOS-ND     | \$0.29                                                                                                                                       |

| 5v Phase locked loop                                         | MM74HC4046N      |             | U19                                       | 512-MM74HC4046N    | INIC 14040BCF03-IND |                                                                                                                                              |

| Quad D-Type Flip Flop                                        |                  |             |                                           | 595-SN74LS175N     |                     | \$0.45                                                                                                                                       |

|                                                              | 74LS175          |             | U2,U12,U24                                | 595-SIN/4LS1/5IN   | 000 4575 5 ND       | \$0.45                                                                                                                                       |

| 3 to 8 Line decoder/demultiplexer; Inverting                 | 74HC138N         |             | U3,U4                                     |                    | 296-1575-5-ND       | \$0.27                                                                                                                                       |

| Quad 2-input NOR gate                                        | 74LS02N          |             | U8                                        |                    | 296-1627-5-ND       | \$0.39                                                                                                                                       |

| Dual J-K Flip Flop                                           | HD74LS73P        |             | U16,U20                                   | 526-NTE74LS73      |                     | \$1.38                                                                                                                                       |

| 4-bit binary counter                                         | 74LS93           |             | U9,U25                                    |                    | 296-3750-5-ND       | \$0.94                                                                                                                                       |

| quadruple 2-input positive NAND gate                         | HD74LS00P        |             | U13,U21,U67,U69                           |                    | 296-1626-5-ND       | \$0.29                                                                                                                                       |

| dual 1-of-4 Decoder/Demultiplexer                            | SN74LS139N       |             | U22                                       | 595-SN74LS139AN    |                     | \$0.38                                                                                                                                       |

| quad 2-input multiplexer                                     | 74LS158          |             | U23                                       | 526-NTE74LS158     |                     | \$1.22                                                                                                                                       |

| triple 3-input NAND gate                                     | 74HC10           |             | U11                                       | 511-M74HC10        |                     | \$0.20                                                                                                                                       |

| Octal 3-state buffer/line-driver                             | SN74LS244N       |             | U14,U26,U29,U49,U68                       |                    | 296-1653-5-ND       | \$0.45                                                                                                                                       |

| Octal D-type Flip Flop, positive edge trigger, 3-state       | 74HCT374N        |             | U27,U48                                   |                    | 568-1543-5-ND       | \$0.30                                                                                                                                       |

| Hex Buffer/Driver with open-collector high voltage Outputs   | SN7407N          |             | U5                                        |                    | 296-1436-5-ND       | \$0.80                                                                                                                                       |

| Octal 3-state buffer/line-driver                             | SN74LS240N       | 1           | U28                                       |                    | 296-1651-5-ND       | \$0.60                                                                                                                                       |

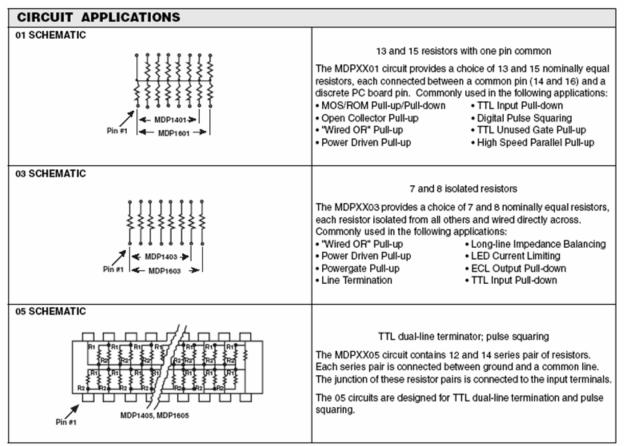

| 8 resistor network (isolated)                                | MDP1603-330G     | 1           | U47                                       | 71-MDP1603-33      |                     | \$0.52                                                                                                                                       |

| 16pin resistor network, dual-line terminated, pulse squaring | MDP1605 221/331G | 1           | U50                                       | 71-MDP1605131AGD04 | 4116R-3-221/331-ND  | \$1.03                                                                                                                                       |

| 27128 EPROM                                                  |                  | 1           | U15                                       |                    |                     |                                                                                                                                              |

| 6551 UART                                                    |                  | 1           | U6                                        |                    |                     |                                                                                                                                              |

|                                                              |                  |             |                                           |                    |                     |                                                                                                                                              |

| DIP SOCKET, 14PIN                                            |                  | 25          |                                           | 517-ICO-143-S8A-T  |                     | \$0.08                                                                                                                                       |

| DIP SOCKET, 16 PIN                                           |                  | 10          |                                           | 517-ICO-163-S8A-T  |                     | \$0.11                                                                                                                                       |

| DIP SOCKET, 20 PIN                                           |                  | 9           |                                           | 517-ICO-203-S8A-T  |                     | \$0.11                                                                                                                                       |

| DIP SOCKET, 28 PIN                                           |                  | 2           |                                           | 517-ICO-286-S8A-T  |                     | \$0.15                                                                                                                                       |

| 25x2 Pin Header, Right angle                                 |                  | 1           |                                           |                    | A32706-25-ND        | \$1.74                                                                                                                                       |

| 25x2 Pin header                                              |                  | 4           |                                           |                    | A32707-25-ND        | \$2.12                                                                                                                                       |

| Female DB9 connector                                         |                  |             | J8                                        | 152-3409           | 102101 20112        | \$0.73                                                                                                                                       |

| Male DB9 Connector                                           |                  |             | J3                                        | 152-3309           |                     | \$0.77                                                                                                                                       |

| Female DB25 connector                                        |                  |             | J2                                        | 152-3425           |                     | \$1.19                                                                                                                                       |

| Power connector                                              |                  |             | J6                                        | 132-3423           | CP-102AH-ND         | \$0.36                                                                                                                                       |

| Power switch                                                 |                  |             | S1                                        | 611-7101-061       | CF-102AII-IND       | \$3.90                                                                                                                                       |

| Red LED                                                      |                  |             | DS2                                       | 606-4305H1         |                     | \$0.21                                                                                                                                       |

| Green LED                                                    |                  |             | DS1                                       | 606-4305H5         |                     | \$0.21                                                                                                                                       |

| Oscillator                                                   | 1.8432mhz        |             | Y1                                        |                    |                     | \$0.21                                                                                                                                       |

| Oscillator                                                   | 1.043211112      |             |                                           | 815-AB-1.8432-B2   |                     | φ1.00                                                                                                                                        |

| anna àr anna air an Aileann Ar E                             | 404/45-          | 05          | -4 -5 -7 -40 -40 -00 -00 -44 - 47 -00 -00 |                    | 2000 1000 NID       | <u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u><u></u></u> |

| capacitor, ceramic,multilayer, .1uF                          | 104/15z          | 35          | c1-c5,c7-c16,c19-c29,c39-c41,c47,c68,c69  |                    | 399-4209-ND         | \$0.05                                                                                                                                       |

|                                                              | 000/DEK          |             | -40 -00 -45 014                           |                    | 000 4047 ND         | <b>CO 10</b>                                                                                                                                 |

| capacitor, ceramic ,multilayer, 68pF                         | 680/R5K          | 6           | c18,c30,c45,CV1                           |                    | 399-4247-ND         | \$0.16                                                                                                                                       |

|                                                              |                  |             | -                                         |                    |                     |                                                                                                                                              |

| capacitor, ceramic,multilayer, .01uF                         | 103/R5M          | 1           | c6                                        |                    | 399-4208-ND         | \$0.12                                                                                                                                       |

|                                                              |                  |             |                                           |                    |                     |                                                                                                                                              |

| capacitor, mica, 22pF                                        | 220/J5           | 1           | c17                                       |                    | 399-4220-ND         | \$0.21                                                                                                                                       |

|                                                              |                  |             |                                           |                    |                     |                                                                                                                                              |

| capacitor,ceramic,multilayer , 470pF                         | 471k/5a          | 2           | c44,c48                                   |                    | 399-4242-ND         | \$0.13                                                                                                                                       |

|                                                              |                  |             |                                           |                    |                     |                                                                                                                                              |

| capacitor, electrolytic                                      | 3300uf,16v       |             | c46                                       |                    | 4043PHBK-ND         | \$2.08                                                                                                                                       |

| capacitor, electrolytic                                      | 220uf,25v        | 2           | c42,c43                                   |                    | 493-1319-ND         | \$0.27                                                                                                                                       |

| resistor                                                     | 1k,1/4w          |             | r4-r8,r10,r11                             |                    | 1.0KQBK-ND          | \$0.01                                                                                                                                       |

| resistor                                                     | 100k,1/4w        |             | r15                                       |                    | 100KQBK-ND          | \$0.02                                                                                                                                       |

| resistor                                                     | 2.2k,1/4w        | 1           | r13                                       |                    | 2.2KQBK-ND          | \$0.02                                                                                                                                       |

| resistor                                                     | 220,1/4w         | 2           | r16,r17                                   |                    | 220QBK-ND           | \$0.02                                                                                                                                       |

| resistor                                                     | 22k,1/4w         |             | r1-r3,r9,r14                              |                    | 22KQBK              | \$0.02                                                                                                                                       |

| resistor                                                     | 470,1/4w         |             | r18                                       | 1                  | 470QBK-ND           | \$0.02                                                                                                                                       |

| resistor                                                     | 100,1/4w         |             | r19                                       | 1                  | 100QBK-ND           | \$0.02                                                                                                                                       |

| resistor                                                     | 4.7k,1/4w        |             | r12,r20-r23                               | 1                  | 3.7KQBK-ND          | \$0.02                                                                                                                                       |

| signal diode                                                 | 1N4/148/H        |             | d1,d6,d7,d8,d9                            | 78-1N4148          |                     | \$0.02                                                                                                                                       |

| rectifier diode                                              | DT/1N4003        |             | d2-d5                                     |                    |                     | ,                                                                                                                                            |

|                                                              |                  |             |                                           | 1                  |                     |                                                                                                                                              |

| voltage regulator                                            | 7805A            | 1           | VR1                                       | 511-L7805ABP       |                     | \$0.47                                                                                                                                       |

| voltage regulator                                            | 428/340LA/15     |             | VR2                                       | 512-MC78L15ACP     |                     | \$0.47                                                                                                                                       |

|                                                              | 720/340LAV 13    | +           | V 1 \ Z                                   | 1512-WIGTOL ISAUF  |                     | φ0.20                                                                                                                                        |

| Variable Capacitor (obsolete- replaced with two 68pF caps)   |                  | 4           | CV1                                       | 659-GKG30015       |                     | \$0.21                                                                                                                                       |

| Inductor, Ceramic                                            | 27uH, 10%        |             | L1,L2                                     | 000-010010         | M8030-ND            | \$0.21                                                                                                                                       |

| 50 conductor Card-edge crimp connector                       | ∠1UΠ, 1070       | Z           | used to make MIO-ATARI cable              |                    | CCE50G-ND           | \$0.52<br>\$4.79                                                                                                                             |

|                                                              |                  | 1           | used to make MIO-ATAKI Cable              | 1                  | 0.4.5000-000        |                                                                                                                                              |

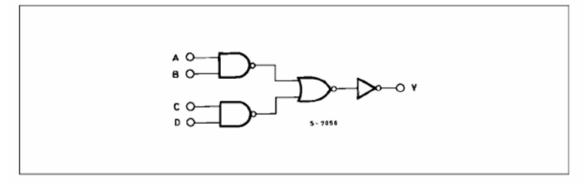

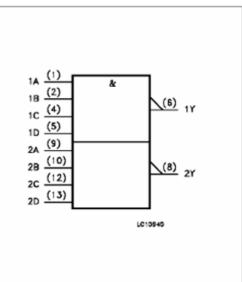

## U1 74LS20 DUAL 4-INPUT NAND GATE PIN CONNECTIONS (top view)

#### Vcc 1A F 18 2 20 NC 5 2C 10 4 NC 6 10 20 . 1 Y ZA GND 7 27

## TRUTH TABLE

| Α | В | С | D | Y |

|---|---|---|---|---|

| L | Х | Х | Х | н |

| Х | L | Х | Х | Н |

| Х | Х | L | Х | Н |

| Х | Х | Х | L | Н |

| Н | н | н | н | L |

### PIN DESCRIPTION

| PIN No | SYMBOL   | NAME AND FUNCTION       |

|--------|----------|-------------------------|

| 1, 9   | 1A to 2A | Data Inputs             |

| 2, 10  | 1B to 2B | Data Inputs             |

| 3, 11  | N. C.    | Not Connected           |

| 4, 12  | 1C, 2C   | Data Inputs             |

| 5, 13  | 1D, 2D   | Data Inputs             |

| 6, 8   | 1Y to 2Y | Data Outputs            |

| 7      | GND      | Ground (0V)             |

| 14     | Vcc      | Positive Supply Voltage |

## SCHEMATIC CIRCUIT (Per Gate)

IEC LOGIC SYMBOL

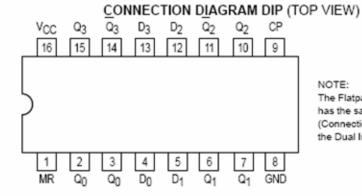

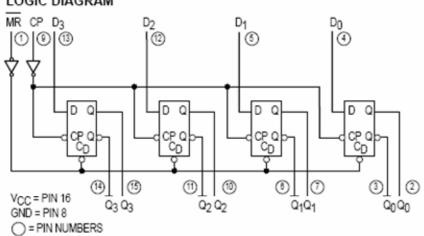

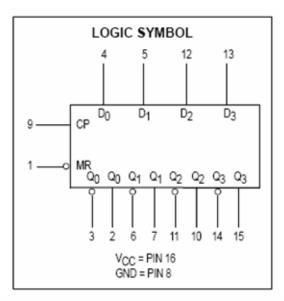

# U2, U12, U24 74LS175 QUAD D FLIP-FLOP

NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package.

| HIGH         LOW           D0-D3         Data Inputs         0.5 U.L.         0.25 U.L.           CP         Clock (Active HIGH Going Edge) Input         0.5 U.L.         0.25 U.L.           MR         Master Reset (Active LOW) Input         0.5 U.L.         0.25 U.L.           Q0-Q3         True Outputs (Note b)         10 U.L.         5 (2.5) U.L.           Q0-Q3         Complemented Outputs (Note b)         10 U.L.         5 (2.5) U.L. | PIN NAMES           | 5                                                                                                | LOADIN                          | G (Note a)                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------|

| CP         Clock (Active HIGH Going Edge) Input         0.5 U.L.         0.25 U.L.           MR         Master Reset (Active LOW) Input         0.5 U.L.         0.25 U.L.           Q0-Q3         True Outputs (Note b)         10 U.L.         5 (2.5) U.L.                                                                                                                                                                                              |                     |                                                                                                  | HIGH                            | LOW                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MR<br><u>Q</u> 0-Q3 | Clock (Active HIGH Going Edge) Input<br>Master Reset (Active LOW) Input<br>True Outputs (Note b) | 0.5 U.L.<br>0.5 U.L.<br>10 U.L. | 0.25 U.L.<br>0.25 U.L.<br>5 (2.5) U.L. |

NOTES:

a. 1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

## LOGIC DIAGRAM

#### FUNCTIONAL DESCRIPTION

The LS175 consists of four edge-triggered D flip-flops with individual D inputs and Q and Q outputs. The Clock and Master Reset are common. The four flip-flops will store the state of their individual D inputs on the LOW to HIGH Clock (CP) transition, causing individual Q and Q outputs to follow. A LOW input on the Master Reset ( $\overline{\text{MR}}$ ) will force all Q outputs LOW and Q outputs HIGH independent of Clock or Data inputs.

The LS175 is useful for general logic applications where a common Master Reset and Clock are acceptable.

TRUTH TABLE

| Inputs (t = n, $\overline{MR}$ = H) | Outputs (t = | n+1) Note 1 |

|-------------------------------------|--------------|-------------|

| D                                   | Q            | Q           |

| L                                   | L            | н           |

| Н                                   | н            | L           |

Note 1: t = n + 1 indicates conditions after next clock.

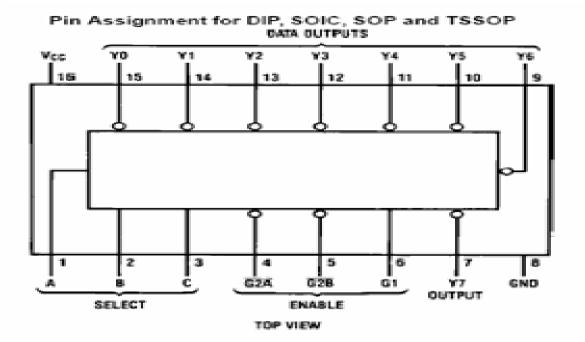

# U3, U4 74LS138 3-TO-8 LINE DECODER

## **Truth Table**

|    | Input       | 5 |        |   |    |    |    | Out | puts |    |    |    |

|----|-------------|---|--------|---|----|----|----|-----|------|----|----|----|

|    | Enable      |   | Select | : |    |    |    |     |      |    |    |    |

| G1 | G2 (Note 1) | С | в      | А | Y0 | Y1 | Y2 | Y3  | Y4   | Y5 | Y6 | Y7 |

| х  | н           | Х | Х      | Х | н  | н  | н  | н   | н    | н  | н  | н  |

| L  | х           | х | х      | х | н  | н  | н  | н   | н    | н  | н  | н  |

| н  | L           | L | L      | L | L  | н  | н  | н   | н    | н  | н  | н  |

| н  | L           | L | L      | н | н  | L  | н  | н   | н    | н  | н  | н  |

| н  | L           | L | н      | L | н  | н  | L  | н   | н    | н  | н  | н  |

| н  | L           | L | н      | н | н  | н  | н  | L   | н    | н  | н  | н  |

| н  | L           | н | L      | L | н  | н  | н  | н   | L    | н  | н  | н  |

| н  | L           | н | L      | н | н  | н  | н  | н   | н    | L  | н  | н  |

| н  | L           | н | н      | L | н  | н  | н  | н   | н    | н  | L  | н  |

| н  | L           | н | н      | н | н  | н  | н  | н   | н    | н  | н  | L  |

H = HIGH Level, L = LOW Level, X = don't care

Note 1: G2 - G2A+G2B

Logic Diagram

logic diagram, each buffer/driver (positive logic)

schematic

# U6 6551 ASYNCHRONOUS COMMUNICATION INTERFACE ADAPTER (ACIA)

## Features

- On-chip baud rate generator: 15 programmable baud rates derived from a standard 1.8432 MHz external crystal (50 to 19,200 baud).

- Programmable interrupt and status register to simplify software design.

- Single +5 volt power supply.

- Serial echo mode.

- False start bit detection.

- 8-bit bi-directional data bus for direct communication with the microprocessor.

- External 16x clock input for non-standard baud rates (up to 125 Kbaud).

- Programmable: word lengths; number of stop bits; and parity bit generation and detection.

- · Data set and modem control signals provided.

- Parity: (odd, even, none, mark, space).

- Full-duplex or half-duplex operation.

- 5, 6, 7, 8 and 9 bit transmission.

## Description

The SY6551 is an Asynchronous Communication Adapter (ACIA) intended to provide for interfacing the 6500/ 6800 microprocessor families to serial communication data sets and modems. A unique feature is the inclusion of an on-chip programmable baud rate generator, with a crystal being the only external component required.

## Pin Configuration

|                 |    | 6551   |    |                   |

|-----------------|----|--------|----|-------------------|

|                 | 1  | $\sim$ | 28 | b ®⁄₩             |

| cs, [           | 2  |        | 27 | D #2              |

| cs, 🗆           | 3  |        | 26 | D IRO             |

| RES             | 4  |        | 25 | Б ов,             |

| RxC             | 5  |        | 24 |                   |

| XTAL1           | 6  |        | 23 | D OB5             |

| XTAL2           | 7  |        | 22 |                   |

| RTS [           | 8  |        | 21 | DB3               |

| CTS [           | 9  |        | 20 |                   |

| TxD 🗌           | 10 |        | 19 | D DB,             |

| DTR C           | 11 |        | 18 | DB0               |

| RxD [           | 12 |        | 17 | DSR               |

| RS <sub>0</sub> | 13 |        | 16 | D DCD             |

| RS <sub>1</sub> | 14 |        | 15 | □ v <sub>cc</sub> |

## Block Diagram

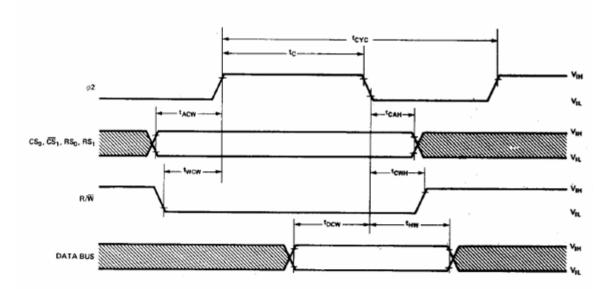

Figure 2. Write Timing Characteristics

| Write Cycle $(V_{CC} = 5.0V \pm 5\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, \text{ un})$ | nless otherwise noted) |

|-------------------------------------------------------------------------------------------|------------------------|

|-------------------------------------------------------------------------------------------|------------------------|

|                      |        | SY6551 |     | SY6 | 551A |      |

|----------------------|--------|--------|-----|-----|------|------|

| Characteristic       | Symbol | Min    | Max | Min | Max  | Unit |

| Cycle Time           | tcyc   | 1.0    | -   | 0.5 | -    | μs   |

| ¢2 Pulse Width       | tc     | 400    | -   | 200 | -    | ns   |

| Address Set-Up Time  | tacw   | 120    | -   | 70  | -    | ris  |

| Address Hold Time    | tCAH   | 0      | -   | 0   | -    | 'ns  |

| R/W Set-Up Time      | twcw   | 120    | -   | 70  | -    | ns   |

| R/W Hold Time        | tсwн   | 0      | -   | 0   | -    | ns   |

| Data Bus Set-Up Time | tDCW   | 150    | -   | 60  | -    | ns   |

| Data Bus Hold Time   | thw    | 20     | -   | 20  | _    | ns   |

$(t_r \text{ and } t_f = 10 \text{ to } 30 \text{ ns})$

## **Crystal Specification**

- 1. Temperature stability ± 0.01% (0° to 70°C)

- 2. Characteristics at 25°C ± 2°C a. Frequency (MHz) 1.8432 b. Frequency tolerance (±%) 0.02 c. Resonance mode Series d. Equivalent resistance (ohm) 400 max. e. Drive level mW 2 f. Shunt capacitance pF 7 max. g. Oscillation mode Fundamental

No other external components should be in the crystal circuit

## **Clock Generation**

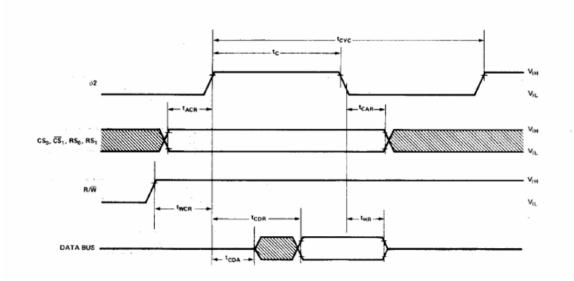

Figure 3. Read Timing Characteristics

| Read Cycle () | $V_{CC} = 5.0V \pm 5\%$ , Ta | $= 0$ to $70^{\circ}$ C. | unless otherwise noted) |

|---------------|------------------------------|--------------------------|-------------------------|

|---------------|------------------------------|--------------------------|-------------------------|

|                                |                  | SY6551 |     | SY6551A |     |      |

|--------------------------------|------------------|--------|-----|---------|-----|------|

| Characteristic                 | Symbol           | Min    | Max | Min     | Max | Unit |

| Cycle Time                     | tcyc             | 1.0    | -   | 0.5     | -   | μs   |

| Pulse Width (¢2)               | tc               | 400    | -   | 200     | -   | ns   |

| Address Set-Up Time            | tACR             | 120    | -   | 70      | -   | ns   |

| Address Hold Time              | tCAR             | 0      | -   | 0       | -   | ns   |

| R/W Set-Up Time                | twcr             | 120    | -   | 70      | -   | ns   |

| Read Access Time (Valid Data)  | t <sub>CDR</sub> | -      | 200 | -       | 150 | ns   |

| Read Data Hold Time            | tHR              | 20     | -   | 20      | -   | ns   |

| Bus Active Time (Invalid Data) | <sup>t</sup> CDA | 40     | -   | 40      | -   | ns   |

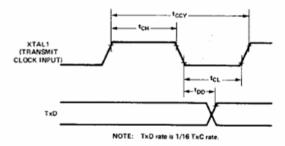

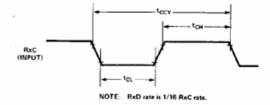

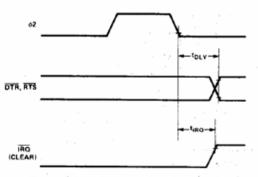

#### Figure 4a. Transmit Timing with External Clock

Figure 4c. Receive External Clock Timing

### **Transmit/Receive Characteristics**

|                                  |                 | SY6551 |     | SY6551A |     |      |

|----------------------------------|-----------------|--------|-----|---------|-----|------|

| Characteristic                   | Symbol          | Min*   | Max | Min     | Max | Unit |

| Transmit/Receive Clock Rate      | tccy            | 400*   | -   | 400*    | · _ | ns   |

| Transmit/Receive Clock High Time | tсн             | 175    | -   | 175     | -   | ns   |

| Transmit/Receive Clock Low Time  | t <sub>CL</sub> | 175    | -   | 175     | -   | ns   |

| XTAL1 to TxD Propagation Delay   | t <sub>DD</sub> | -      | 500 |         | 500 | ns   |

| Propagation Delay (RTS, DTR)     | tDLY            | -      | 500 | -       | 500 | ns   |

| IRQ Propagation Delay (Clear)    | tiRQ            | -      | 500 | -       | 500 | ns   |

(tr, tr = 10 to 30 ns input clocks only)

\*The baud rate with external clocking is:

Baud Rate = 16 x TCCY

1

## Interface Signal Description

#### RES (Reset)

During system initialization a low on the RES input will cause internal registers to be cleared.

#### \$\$\phi\$2 (Input Clock)

The input clock is the system  $\phi 2$  clock and is used to trigger all data transfers between the system microprocessor and the SY6551.

#### R/W (Read/Write)

The  $R/\overline{W}$  is generated by the microprocessor and is used to control the direction of data transfers. A high on the  $R/\overline{W}$  pin allows the processor to read the data supplied by the SY6551. A low on the  $R/\overline{W}$  pin allows a write to the SY6551.

### IRO (Interrupt Request)

The IRQ pin is an interrupt signal from the interrupt control logic. It is an open drain output, permitting

several devices to be connected to the common  $\overline{IRQ}$  microprocessor input. Normally a high level,  $\overline{IRQ}$  goes low when an interrupt occurs.

### DB<sub>0</sub> - DB<sub>7</sub> (Data Bus)

The DB<sub>0</sub>-DB<sub>7</sub> pins are the eight data lines used for transfer of data between the processor and the SY6551. These lines are bi-directional and are normally high-impedance except during Read cycles when selected.

### CS0, CS1 (Chip Selects)

The two chip select inputs are normally connected to the processor address lines either directly or through decoders. The SY6551 is selected when  $CS_0$  is high and  $\overline{CS}_1$  is low.

#### RSd, RS1 (Register Selects)

The two register select lines are normally connected to the processor address lines to allow the processor to select the various SY6551 internal registers. The following table indicates the internal register select coding:

| RS <sub>1</sub> | RS <sub>0</sub> | Write                                                         | Read                      |  |  |

|-----------------|-----------------|---------------------------------------------------------------|---------------------------|--|--|

| 0               | 0               | Transmit Data<br>Register                                     | Receiver Data<br>Register |  |  |

| 0               | 1               | Programmed Status Register<br>Reset (Data is<br>"Don't Care") |                           |  |  |

| 1               | 0               | Command Register                                              |                           |  |  |

| 1               | 1               | Control Register                                              |                           |  |  |

The table shows that only the Command and Control registers are read/write. The Programmed Reset operation does not cause any data transfer, but is used to clear the SY6551 registers. The Programmed Reset is slightly different from the Hardware Reset ( $\overline{RES}$ ) and these differences are described in the individual register definitions.

## ACIA/Modern Interface Signal Description

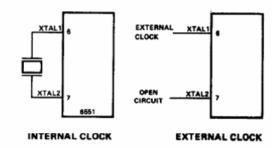

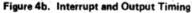

#### XTAL1, XTAL2 (Crystal Pins)

These pins are normally directly connected to the external crystal (1.8432 MHz) used to derive the various baud rates. Alternatively, an externally generated clock may be used to drive the XTAL1 pin, in which case the XTAL2 pin must float.

#### TxD (Transmit Data)

The TxD output line is used to transfer serial NRZ (nonreturn-to-zero) data to the modem. The LSB (least significant bit) of the Transmit Data Register is the first data bit transmitted and the rate of data transmission is determined by the baud rate selected.

#### RxD (Receive Data)

The RxD input line is used to transfer serial NRZ data into the ACIA from the modem, LSB first. The receiver data rate is either the programmed baud rate or the rate of an externally generated receiver clock. This selection is made by programming the Control Register.

#### RxC (Receive Clock)

The RxC is a bi-directional pin which serves as either the receiver 16x clock input or the receiver 16x clock output. The latter mode results if the internal baud rate generator is selected for receiver data clocking.

#### RTS (Request to Send)

The  $\overline{RTS}$  output pin is used to control the modem from the processor. The state of the  $\overline{RTS}$  pin is determined by the contents of the Command Register.

#### CTS (Clear to Send)

The CTS input pin is used to control the transmitter operation. The enable state is with CTS low. The transmitter is automatically disabled if CTS is high.

#### DTR (Data Terminal Ready)

This output pin is used to indicate the status of the SY6551 to the modem. A low on  $\overline{\text{DTR}}$  indicates the SY6551 is enabled and a high indicates it is disabled. The processor controls this pin via bit 0 of the Command Register.

### DSR (Data Set Ready)

The DSR input pin is used to indicate to the SY6551 the status of the modem. A low indicates the "ready" state and a high, "not-ready." DSR is a high-impedance input and must not be a no-connect. If unused, it should be driven high or low, but not switched.

Note: If Command Register Bit 0 = 1 and a change of state on DSR occurs, IRQ will be set, and Status Register Bit 6 will reflect the new level. The state of DSR does not affect either Transmitter or Receiver operation.

### DCD (Data Carrier Detect)

The  $\overline{DCD}$  input pin is used to indicate to the SY6551 the status of the carrier-detect output of the modern. A low indicates that the modern carrier signal is present and a high, that it is not.  $\overline{DCD}$ , like  $\overline{DSR}$ , is a high-impedance input and must not be a no-connect.

Note: If Command Register Bit 0 = 1 and a change of state on DCD occurs, IRQ will be set, and Status Register Bit 5 will reflect the new level. The state of DCD does not affect Transmitter operation, but must be low for the Receiver to operate.

### Internal Organization

The Transmitter/Receiver sections of the SY6551 are depicted by the block diagram in Figure 5.

Figure 5. Transmitter/Receiver Clock Circuits

Bits 0-3 of the Control Register select the divisor used to generate the baud rate for the Transmitter. If the Receiver clock is to use the same baud rate as the Transmitter, then RxC becomes an output pin and can be used to slave other circuits to the SY6551.

## **Control Register**

The Control Register is used to select the desired mode for the SY6551. The word length, number of stop bits, and clock controls are all determined by the Control Register, which is depicted in Figure 6.

Figure 6. Control Register Format

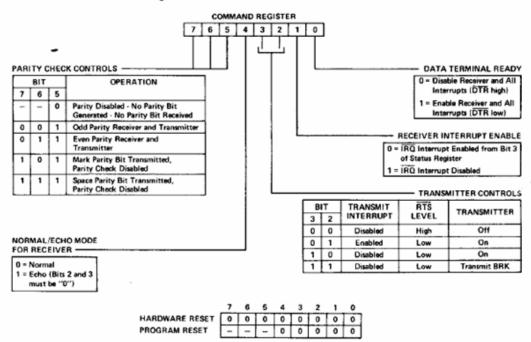

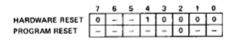

## **Command Register**

The Command Register is used to control Specific Transmit/Receive functions and is shown in Figure 7.

Figure 7. Command Register Format

## **Status Register**

The Status Register is used to indicate to the processor the status of various SY6551 functions and is outlined in Figure 8.

| 76543210 |                                 |                                    |                                         |

|----------|---------------------------------|------------------------------------|-----------------------------------------|

|          | STATUS                          | SET BY                             | CLEARED BY                              |

|          | Parity Error*                   | 0 = No Error<br>1 = Error          | Self Clearing**                         |

|          | Framing Error*                  | 0 = No Error<br>t = Error          | Self Clearing**                         |

|          | Overrun*                        | 0 = No Error<br>1 - Error          | Self Clearing**                         |

|          | Receive Data<br>Register Full   | 0 = Not Full<br>1 - Full           | Read Receive<br>Data Register           |

|          | Transmit Data<br>Register Empty | 0 - Not Empty<br>1 = Empty         | Write Transmit<br>Data Register         |

|          | DCD                             | 0 = DCD Low<br>1 = DCD High        | Not Resettable<br>Reflects DCD<br>State |

|          | DSR                             | 0 = <u>DSR</u> Low<br>1 = DSR High | Not Resettable<br>Reflects DSR<br>State |

|          | IRQ                             | 0 = No Interrupt<br>1 = Interrupt  | Read<br>Status Register                 |

•NO INTERRUPT GENERATED FOR THESE CONDITIONS. •\*CLEARED AUTOMATICALLY AFTER A READ OF RDR AND THE NEXT ERROR FREE RECEIPT OF DATA.

Figure 8. Status Register Format

## **Transmit and Receive Data Registers**

These registers are used as temporary data storage for the 6551 Transmit and Receive circuits. The Transmit Data Register is characterized as follows:

- · Bit 0 is the leading bit to be transmitted.

- Unused data bits are the high-order bits and are "don't care" for transmission.

The Receive Data Register is characterized in a similar fashion:

- Bit 0 is the leading bit received.

- Unused data bits are the high-order bits and are "0" for the receiver.

- Parity bits are not contained in the Receive Data Register, but are stripped-off after being used for external parity checking. Parity and all unused high-order bits are "0".

Figure 9 illustrates a single transmitted or received data word, for the example of 8 data bits, parity, and 1 stop bit.

Figure 9. Serial Data Stream Example

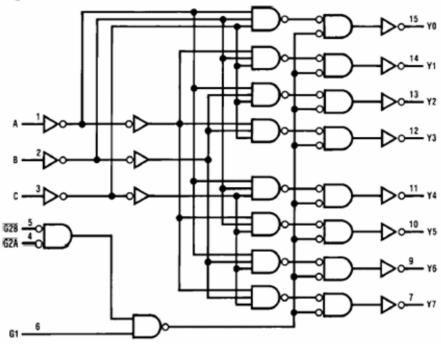

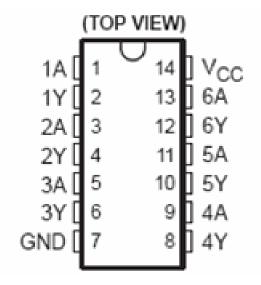

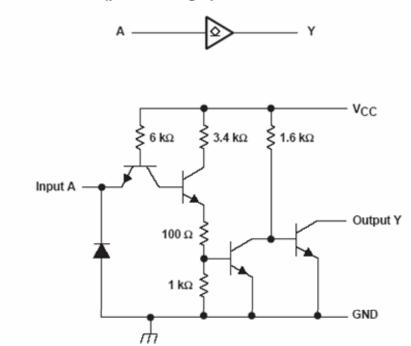

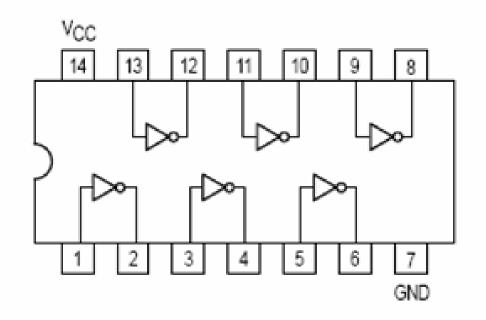

U7, U10 74LS04 HEX INVERTER

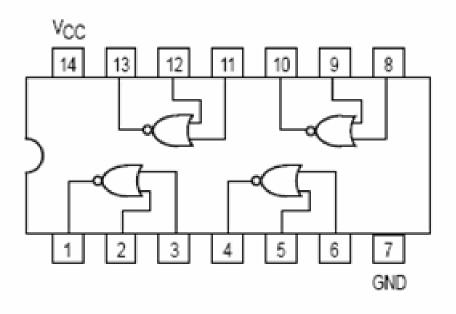

# U8 74LS02 QUAD 2-INPUT NOR GATE

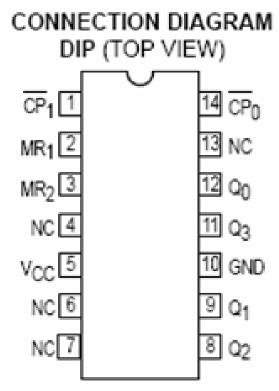

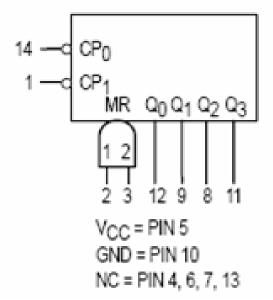

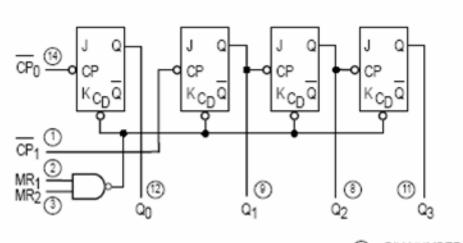

# U9, U25 74LS93 4-BIT BINARY COUNTER

| NC = NO INTERNAL CONNECTION |

|-----------------------------|

|-----------------------------|

| PIN NAMES                                        |                                                                                | LOADING (Note a) |              |  |

|--------------------------------------------------|--------------------------------------------------------------------------------|------------------|--------------|--|

|                                                  |                                                                                | HIGH             | LOW          |  |

| CP0                                              | Clock (Active LOW going edge) Input to<br>+2 Section                           | 0.5 U.L.         | 1.5 U.L.     |  |

| CP1                                              | Clock (Active LOW going edge) Input to<br>+5 Section (LS90), +6 Section (LS92) | 0.5 U.L.         | 2.0 U.L.     |  |

| CP1                                              | Clock (Active LOW going edge) Input to<br>+8 Section (LS93)                    | 0.5 U.L.         | 1.0 U.L.     |  |

| MR <sub>1</sub> , MR <sub>2</sub>                | Master Reset (Clear) Inputs                                                    | 0.5 U.L.         | 0.25 U.L.    |  |

| MS1, MS2                                         | Master Set (Preset-9, LS90) Inputs                                             | 0.5 U.L.         | 0.25 U.L.    |  |

| Q <sub>0</sub>                                   | Output from +2 Section (Notes b & c)                                           | 10 U.L.          | 5 (2.5) U.L. |  |

| Q <sub>1</sub> , Q <sub>2</sub> , Q <sub>3</sub> | Outputs from +5 (LS90), +6 (LS92),<br>+8 (LS93) Sections (Note b)              | 10 U.L.          | 5 (2.5) U.L. |  |

NOTES:

a. 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military, (54) and 5 U.L. for commercial (74) Temperature Ranges.

c. The Q<sub>0</sub> Outputs are guaranteed to drive the full fan-out plus the CP<sub>1</sub> input of the device.

d. To insure proper operation the rise  $(t_{f})$  and fall time  $(t_{f})$  of the clock must be less than 100 ns.

## LOGIC DIAGRAM

LS93

C = PIN NUMBERS V<sub>CC</sub> = PIN 5 GND = PIN 10

| TRUTH TABLE |                |    |    |       |  |  |

|-------------|----------------|----|----|-------|--|--|

| COUNT       | OUTPUT         |    |    |       |  |  |

| COONT       | Q <sub>0</sub> | Q1 | Q2 | $Q_3$ |  |  |

| 0           | L              | L  | L  | L     |  |  |

| 1           | н              | L  | L  | L     |  |  |

| 2           | L              | н  | L  | L     |  |  |

| 3           | н              | н  | L  | L     |  |  |

| 4           | L              | L  | н  | L     |  |  |

| 5           | н              | L  | н  | L     |  |  |

| 6           | L              | н  | н  | L     |  |  |

| 7           | н              | н  | н  | L     |  |  |

| 8           | L              | L  | L  | н     |  |  |

| 9           | н              | L  | L  | н     |  |  |

| 10          | L              | н  | L  | н     |  |  |

| 11          | н              | н  | L  | н     |  |  |

| 12          | L              | L  | н  | н     |  |  |

| 13          | н              | L  | н  | н     |  |  |

| 14          | L              | н  | н  | н     |  |  |

| 15          | н              | н  | н  | н     |  |  |

END DESCRIPTION OF

TADL

NOTE: Output Q0 is connected to Input CP1.

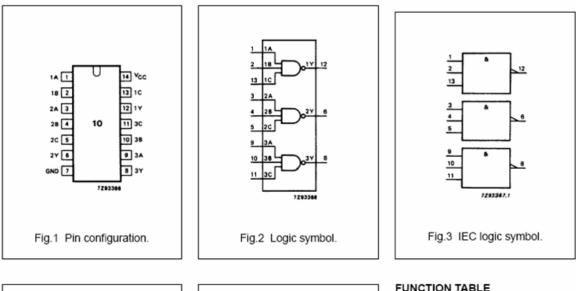

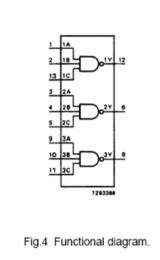

# U11 74LS10 TRIPLE 3-INPUT NAND GATE

## PIN DESCRIPTION

| PIN NO.   | SYMBOL   | NAME AND FUNCTION       |  |

|-----------|----------|-------------------------|--|

| 1, 3, 9   | 1A to 3A | data inputs             |  |

| 2, 4, 10  | 1B to 3B | data inputs             |  |

| 13, 5, 11 | 1C to 3C | data inputs             |  |

| 12, 6, 8  | 1Y to 3Y | data outputs            |  |

| 7         | GND      | ground (0 V)            |  |

| 14        | Vcc      | positive supply voltage |  |

## FUNCTION TABLE

| INPUTS |    | OUTPUT |    |

|--------|----|--------|----|

| nA     | nB | nC     | nY |

| L      | L  | L      | н  |

| L      | L  | н      | н  |

| L      | н  | L      | н  |

| L      | н  | н      | н  |

| н      | L  | L      | н  |

| н      | L  | н      | н  |

| н      | н  | L      | н  |

| н      | н  | н      | L  |

### Notes

1. H = HIGH voltage level L = LOW voltage level

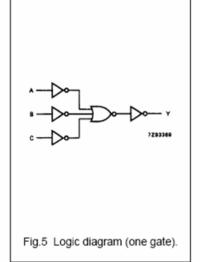

# U13, U21, U67, U69 74LS00 QUAD 2-INPUT NAND GATE

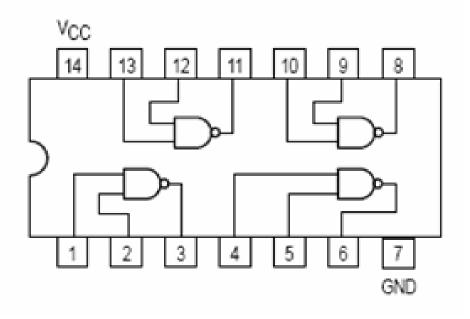

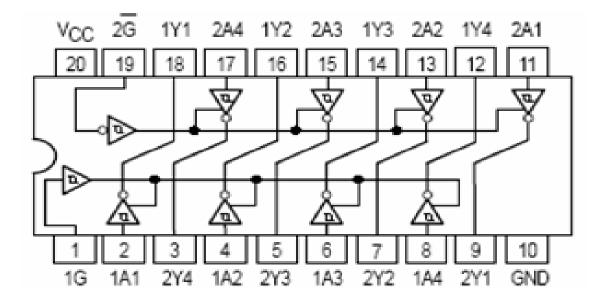

U14, U26, U29, U49, U68 74LS244 OCTAL BUFFER/LINE DRIVER WITH TRI-STATE OUTPUTS

| INPUTS |   | OUTPUT |  |  |

|--------|---|--------|--|--|

| 1G, 2G | D | 001901 |  |  |

| L      | L | L      |  |  |

| L      | н | н      |  |  |

| н      | Х | (Z)    |  |  |

|                                      |                                                | Limits |           |          |      |

|--------------------------------------|------------------------------------------------|--------|-----------|----------|------|

| Symbol                               | Parameter                                      | Min    | Тур       | Мах      | Unit |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay, Data to Output<br>LS240     |        | 9.0<br>12 | 14<br>18 | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay, Data to Output<br>LS241/244 |        | 12<br>12  | 18<br>18 | ns   |

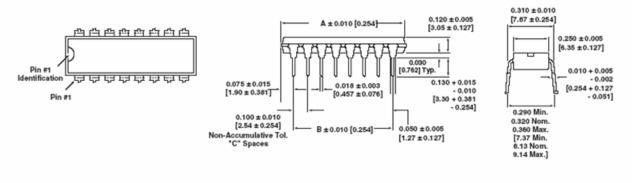

U15 27C128 16K x 8 EPROM

## Block Diagram

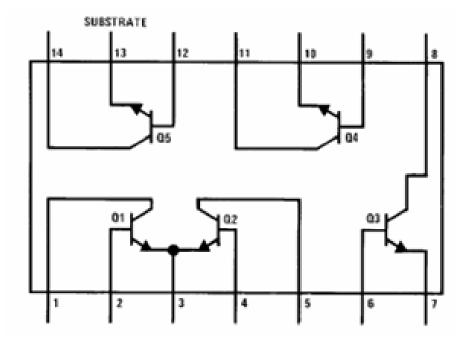

U18 LM3086 TRANSISTOR ARRAY

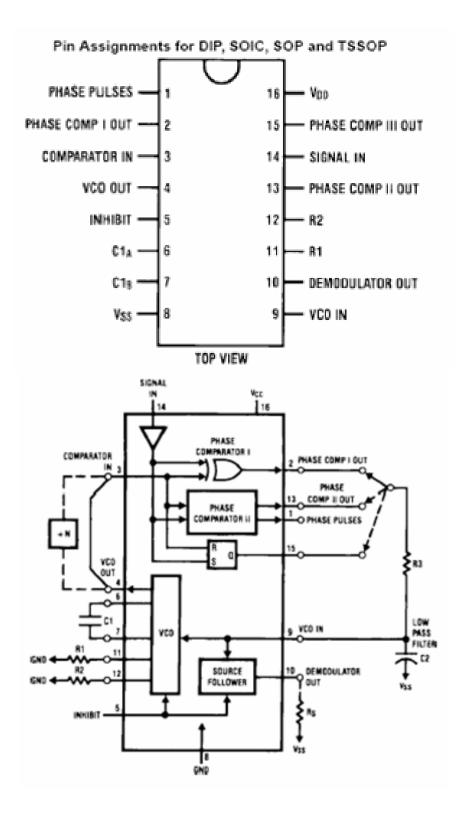

# U19 74HC4046 PHASE LOCKED LOOP

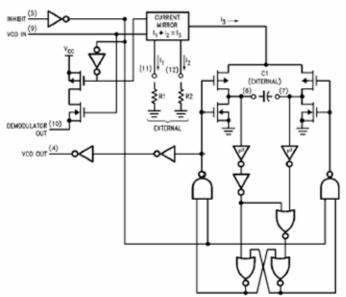

#### VOLTAGE CONTROLLED OSCILLATOR/SOURCE FOLLOWER

The VCO requires two or three external components to operate. These are R1, R2, C1. Resistor R1 and capacitor C1 are selected to determine the center frequency of the VCO. R1 controls the lock range. As R1's resistance decreases the range of  $f_{MIN}$  to  $f_{MAX}$  increases. Thus the VCO's gain increases. As C1 is changed the offset (if used) of R2, and the center frequency is changed. (See typical performance curves) R2 can be used to set the offset frequency with 0V at VCO input. If R2 is omitted the VCO range is from 0Hz. As R2 is decreased the offset frequency is increased. The effect of R2 is shown in the design information table and typical performance curves. By increasing

the value of R2 the lock range of the PLL is offset above OHz and the gain (Hz/Volt) does not change. In general, when offset is desired, R2 and C1 should be chosen first, and then R1 should be chosen to obtain the proper center frequency.

Internally the resistors set a current in a current mirror as shown in Figure 1. The mirrored current drives one side of the capacitor once the capacitor charges up to the threshold of the schmitt trigger the oscillator logic flips the capacitor over and causes the mirror to charge the opposite side of the capacitor. The output from the internal logic is then taken to pin 4.

| Com                       | parator I                                                          | Comparator II & III                                     |                                                                    |  |

|---------------------------|--------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|--|

| R₂≡ ↔                     | R <sub>2</sub> #**                                                 | R₂≡ ↔                                                   | R <sub>2</sub> #**                                                 |  |

| Given: fg                 | •Given: f0 and fL                                                  | •Given: f <sub>MAX</sub>                                | <ul> <li>Given: f<sub>MIN</sub> and f<sub>MAX</sub></li> </ul>     |  |

| Use fo with curve titled  | <ul> <li>Calculate f<sub>MIN</sub> from the</li> </ul>             | <ul> <li>Calculate f<sub>0</sub> from the</li> </ul>    | <ul> <li>Use f<sub>MIN</sub> with curve titled</li> </ul>          |  |

| center frequency vs R1, C | equation $f_{MIN} = f_0 - f_L$                                     | equation $f_0 = f_{MAX}/2$                              | offset frequency vs R2,                                            |  |

| to determine R1 and C1    | <ul> <li>Use f<sub>MIN</sub> with curve titled</li> </ul>          | <ul> <li>Use f<sub>0</sub> with curve titled</li> </ul> | C to determine R2 and C1                                           |  |

|                           | offset frequency vs R2, C                                          | center frequency vs R1, C                               | <ul> <li>Calculate f<sub>MAX</sub>/f<sub>MIN</sub></li> </ul>      |  |

|                           | to determine R2 and C1                                             | to determine R1 and C1                                  | <ul> <li>Use f<sub>MAX</sub>/f<sub>MIN</sub> with curve</li> </ul> |  |

|                           | <ul> <li>Calculate f<sub>MAX</sub>/f<sub>MIN</sub> from</li> </ul> |                                                         | titled f <sub>MAX</sub> /f <sub>MIN</sub> vs R2/R1                 |  |

|                           | the equation f <sub>MAX</sub> /f <sub>MIN</sub> =                  |                                                         | to determine ratio R2/R1                                           |  |

|                           | $f_0 + f_L/f_0 - f_L$                                              |                                                         | to obtain R1                                                       |  |

|                           | <ul> <li>Use f<sub>MAX</sub>/f<sub>MIN</sub> with curve</li> </ul> |                                                         |                                                                    |  |

|                           | titled f <sub>MAX</sub> /f <sub>MIN</sub> vs R2/R1                 |                                                         |                                                                    |  |

|                           | to determine ratio R2/R1                                           |                                                         |                                                                    |  |

|                           | to obtain R1                                                       |                                                         |                                                                    |  |

|                           | FIGU                                                               | RE 1.                                                   | •                                                                  |  |

#### FIGURE 2. Logic Diagram for VCO

The input to the VCO is a very high impedance CMOS input and so it will not load down the loop filter, easing the filters design. In order to make signals at the VCO input accessible without degrading the loop performance a source follower transistor is provided. This transistor can be used by connecting a resistor to ground and its drain output will follow the VCO input signal.

An inhibit signal is provided to allow disabling of the VCO and the source follower. This is useful if the internal VCO is

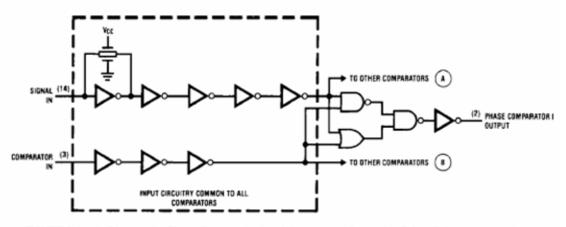

#### PHASE COMPARATORS

All three phase comparators share two inputs, Signal In and Comparator In. The Signal In has a special DC bias network that enables AC coupling of input signals. If the signals are not AC coupled then this input requires logic levels the same as standard 74HC. The Comparator input not being used. A logic high on inhibit disables the VCO and source follower.

The output of the VCO is a standard high speed CMOS output with an equivalent LSTTL fanout of 10. The VCO output is approximately a square wave. This output can either directly feed the comparator input of the phase comparators or feed external prescalers (counters) to enable frequency synthesis.

is a standard digital input. Both input structures are shown in Figure 3.

The outputs of these comparators are essentially standard 74HC voltage outputs. (Comparator II is 3-STATE.)

FIGURE 3. Logic Diagram for Phase Comparator I and the common input circuit for all three comparators

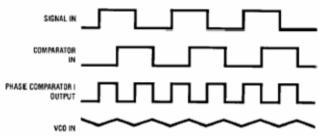

#### FIGURE 4. Typical Phase Comparator I. Waveforms

Thus in normal operation  $V_{CC}$  and ground voltage levels are fed to the loop filter. This differs from some phase detectors which supply a current output to the loop filter and this should be considered in the design. (The CD4048 also provides a voltage.)

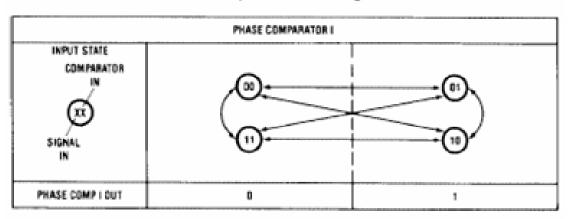

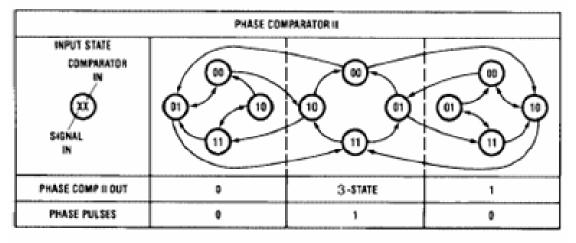

Figure 5 shows the state tables for all three comparators.

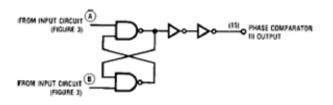

#### PHASE COMPARATOR I

This comparator is a simple XOR gate similar to the 74HC88, and its operation is similar to an overdriven balanced modulator. To maximize lock range the input frequencies must have a 50% duty cycle. Typical input and output waveforms are shown in Figure 4. The output of the phase detector feeds the loop filter which averages the output voltage. The frequency range upon which the PLL will lock onto if initially out of lock is defined as the capture range. The capture range for phase detector I is dependent on the loop filter employed. The capture range can be as large as the lock range which is equal to the VCO frequency range.

To see how the detector operates refer to Figure 4. When two square wave inputs are applied to this comparator, an output waveform whose duty cycle is dependent on the phase difference between the two signals results. As the phase difference increases the output duty cycle increases and the voltage after the loop filter increases. Thus in order to achieve lock, when the PLL input frequency increases the VCO input voltage must increase and the phase difference between comparator in and signal in will increase. At an input frequency equal  $f_{\rm MIN}$ , the VCO input is at 0V and this requires the phase detector output to be ground hence the two input signals must be in phase. When the input fre-

quency is  $f_{MAX}$  then the VCO input must be V<sub>CC</sub> and the phase detector inputs must be 180° out of phase.

The XOR is more susceptible to locking onto harmonics of the signal input than the digital phase detector II. This can be seen by noticing that a signal 2 times the VCO frequency results in the same output duty cycle as a signal equal the VCO frequency. The difference is that the output frequency of the 2f example is twice that of the other example. The loop filter and the VCO range should be designed to prevent locking on to harmonics.

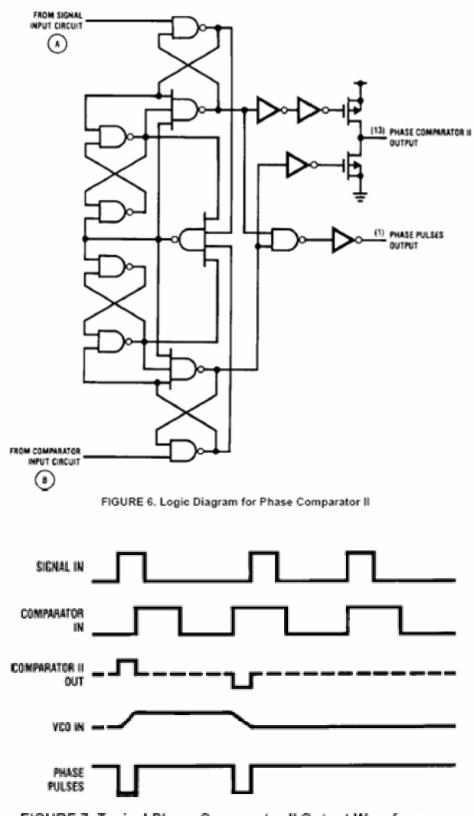

#### PHASE COMPARATOR II

This detector is a digital memory network. It consists of four flip-flops and some gating logic, a three state output and a phase pulse output as shown in Figure 6. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle.

Phase comparator II operates in such a way as to force the PLL into lock with 0 phase difference between the VCO output and the signal input positive waveform edges. Figure 7 shows some typical loop waveforms. First assume that the signal input phase is leading the comparator input. This means that the VCO's frequency must be increased to bring its leading edge into proper phase alignment. Thus the phase detector II output is set high. This will cause the loop filter to charge up the VCO input increasing the VCO frequency. Once the leading edge of the comparator input is detected the output goes 3-STATE holding the VCO input at the loop filter voltage. If the VCO still lags the signal then the phase detector will again charge up to VCO input for the time between the leading edges of both waveforms.

# Phase Comparator State Diagrams

FIGURE 5. PLL State Tables

## Detailed Circuit Description (Continued)

If the VCO leads the signal then when the leading edge of the VCO is seen the output of the phase comparator goes LOW. This discharges the loop filter until the leading edge of the signal is detected at which time the output 3-STATE itself again. This has the effect of slowing down the VCO to again make the rising edges of both waveform coincident.

When the PLL is out of lock the VCO will be running either slower or faster than the signal input. If it is running slower the phase detector will see more signal rising edges and so the output of the phase comparator will be HIGH a majority of the time, raising the VCO's frequency. Conversely, if the VCO is running faster than the signal the output of the detector will be LOW most of the time and the VCO's output frequency will be decreased.

As one can see when the PLL is locked the output of phase comparator II will be almost always 3-STATE except for minor corrections at the leading edge of the waveforms. When the detector is 3-STATE the phase pulse output is HIGH. This output can be used to determine when the PLL is in the locked condition.

This detector has several interesting characteristics. Over the entire VCO frequency range there is no phase difference between the comparator input and the signal input. The lock range of the PLL is the same as the capture range. Minimal power is consumed in the loop filter since in lock the detector output is a high impedance. Also when no signal is present the detector will see only VCO leading edges, and so the comparator output will stay LOW forcing the VCO to f<sub>MIN</sub> operating frequency. Phase comparator II is more susceptible to noise causing the phase lock loop to unlock. If a noise pulse is seen on the signal input, the comparator treats it as another positive edge of the signal and will cause the output to go HIGH until the VCO leading edge is seen, potentially for a whole signal input period. This would cause the VCO to speed up during that time. When using the phase comparator I the output of that phase detector would be disturbed for only the short duration of the noise spike and would cause less upset.

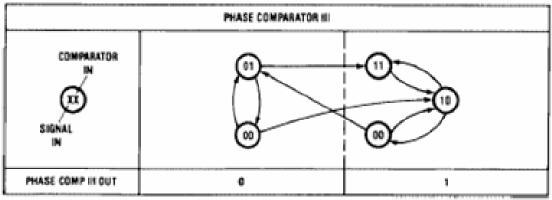

#### PHASE COMPARATOR III

This comparator is a simple S-R Flip-Flop which can function as a phase comparator Figure 8. It has some similar characteristics to the edge sensitive comparator. To see how this detector works assume input pulses are applied to the signal and comparator inputs as shown in Figure 9. When the signal input leads the comparator input the flop is set. This will charge up the loop filter and cause the VCO to speed up, bringing the comparator into phase with the signal input. When using short pulses as input this comparator behaves very similar to the second comparator. But one can see that if the signal input is a long pulse, the output of the comparator will be forced to a one no matter how many comparator input pulses are received. Also if the VCO input is a square wave (as it is) and the signal input is pulse then the VCO will force the comparator output LOW much of the time. Therefore it is ideal to condition the signal and comparator input to short pulses. This is most easily done by using a series capacitor.

FIGURE 8. Phase Comparator III Logic Diagram

FIGURE 9. Typical Waveforms for Phase Comparator III

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b) The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

## LOGIC DIAGRAM

V<sub>CC</sub> = PIN 16 GND = PIN 8

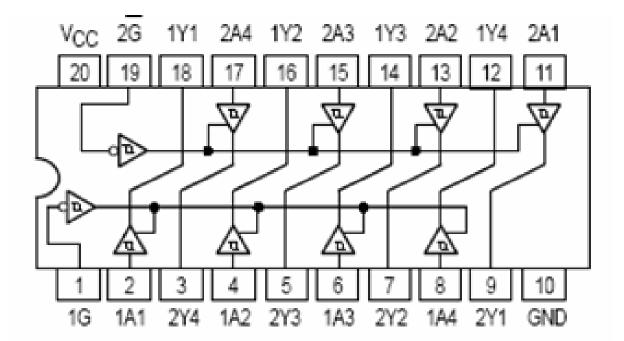

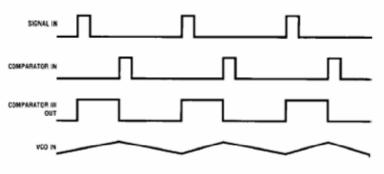

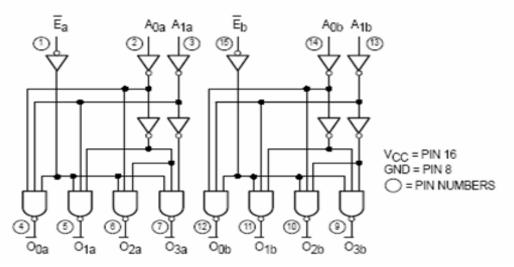

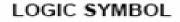

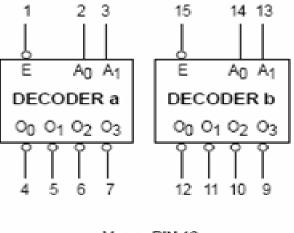

# FUNCTIONAL DESCRIPTION

The LS139 is a high speed dual 1-of-4 decoder/demultiplexer fabricated with the Schottky barrier diode process. The device has two independent decoders, each of which accept two binary weighted inputs (A0.A1) and provide four mutually exclusive active LOW outputs (O0-O3). Each decoder has an active LOW Enable (E). When E is HIGH all outputs are forced HIGH. The enable can be used as the data input for a 4-output demultiplexer application.

Each half of the LS139 generates all four minterms of two variables. These four minterms are useful in some applications, replacing multiple gate functions as shown in Fig. a, and thereby reducing the number of packages required in a logic network.

| TRUTH | TABLE |

|-------|-------|

|-------|-------|

|   | INPUTS         | ;  |    | OUT | PUTS |    |

|---|----------------|----|----|-----|------|----|

| E | A <sub>0</sub> | A1 | 00 | 01  | 02   | 03 |

| Н | Х              | Х  | н  | Н   | Н    | Н  |

| L | L              | L  | L  | н   | н    | н  |

| L | н              | L  | н  | L   | н    | н  |

| L | L              | н  | н  | н   | L    | Н  |

| L | н              | н  | н  | н   | н    | L  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

Figure a

#### PIN NAMES

| LOADING (N | lote a) |

|------------|---------|

|------------|---------|

| S       | Common Select Input       |

|---------|---------------------------|

| E       | Enable (Active LOW) Input |

| l0a-l0d | Data Inputs from Source 0 |

| Lia-Lid | Data Inputs from Source 1 |

| Za-Zd   | Inverted Outputs (Note b) |

| HIGH     | LOW          |

|----------|--------------|

| 1.0 U.L. | 0.5 U.L.     |

| 1.0 U.L. | 0.5 U.L.     |

| 0.5 U.L. | 0.25 U.L.    |

| 0.5 U.L. | 0.25 U.L.    |

| 10 U.L.  | 5 (2.5) U.L. |

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 μA HIGH/1.6 mA LOW.

b) The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

# LOGIC DIAGRAM

# LOGIC SYMBOL

V<sub>CC</sub> = PIN 16 GND = PIN 8

# FUNCTIONAL DESCRIPTION

The LS158 is a Quad 2-input Multiplexer fabricated with the Schottky barrier diode process for high speed. It selects four bits of data from two sources under the control of a common Select Input (S) and presents the data in inverted form at the four outputs. The Enable Input (E) is active LOW. When E is HIGH, all of the outputs (Z) are forced HIGH regardless of all other inputs.

The LS158 is the logic implementation of a 4-pole, 2-position switch where the position of the switch is determined by the logic levels supplied to the Select Input.

A common use of the LS158 is the moving of data from two groups of registers to four common output busses. The particular register from which the data comes is determined by the state of the Select Input. A less obvious use is as a function generator. The LS158 can generate four functions of two variables with one variable common. This is useful for implementing gating functions.

| ENABLE | SELECT<br>INPUT | INPUTS |                | OUTPUT |

|--------|-----------------|--------|----------------|--------|

| E      | S               | I0     | I <sub>1</sub> | Z      |

| н      | х               | Х      | Х              | Н      |

| L      | L               | L      | Х              | н      |

| L      | L               | н      | Х              | L      |

| L      | н               | х      | L              | н      |

| L      | н               | Х      | н              | L      |

| TRI | JTH | TABI | E |

|-----|-----|------|---|

|     |     |      | _ |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

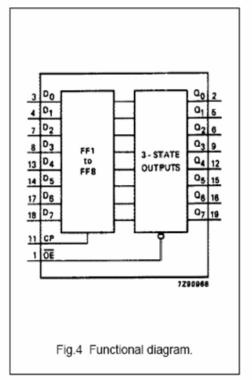

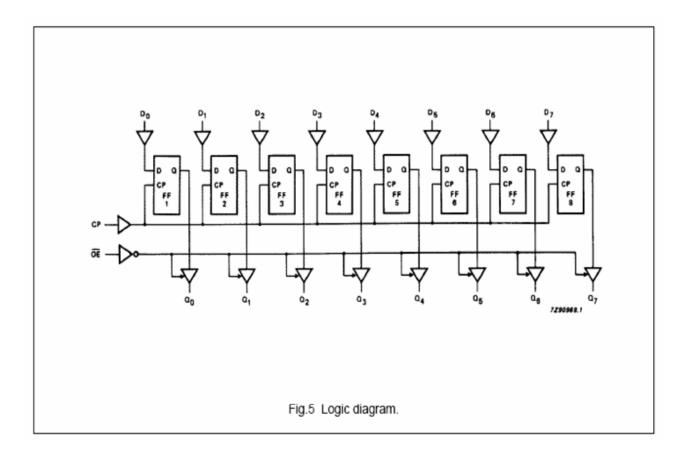

# U27, U48 74LS374 OCTAL D-TYPE FLIP-FLOP; POSITIVE EDGE TRIGGER; TRI-STATE

### PIN DESCRIPTION

| PIN NO.                    | SYMBOL                           | NAME AND FUNCTION                         |

|----------------------------|----------------------------------|-------------------------------------------|

| 1                          | OE                               | 3-state output enable input (active LOW)  |

| 2, 5, 6, 9, 12, 15, 16, 19 | Q <sub>0</sub> to Q <sub>7</sub> | 3-state flip-flop outputs                 |

| 3, 4, 7, 8, 13, 14, 17, 18 | D <sub>0</sub> to D <sub>7</sub> | data inputs                               |

| 10                         | GND                              | ground (0 V)                              |

| 11                         | CP                               | clock input (LOW-to-HIGH, edge-triggered) |

| 20                         | Vcc                              | positive supply voltage                   |