8-Bit High Speed Analog-to-Digital Converter

#### **FEATURES**

- 3 MHz Sampling Rate

- Non-Linearity +1/4 LSB (typ) with S/H

- Low Power CMOS 100mW (typ)

- Requires NO SAMPLE AND HOLD for signals less than 100 kHz

- Single Supply Voltage (+4 V to +6 V)

- Latch-Up Free

#### **APPLICATIONS**

- High Speed Low Power A/D Conversion

- Satellite Operations

- High Energy Physics Research

- Portable Products

- Radar Pulse Analysis

- μP Data Acquisition Systems

#### **GENERAL DESCRIPTION**

The MP7683 is a monolithic CMOS 8-bit two step flash Analog-to-Digital Converter designed for applications which demand Low Power Consumption and High Speed digitization (2 MHz sampling rate, 100mW power dissipation). The linearity error is 1/4 LSB (typical), with clock frequency of 2 MHz at a supply voltage of 5 volts.

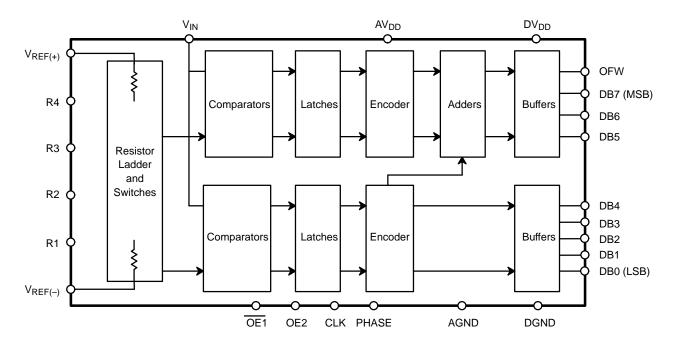

The MP7683 conversion is done in two segments. The first segment converts the 3 MSBs and consists of eight (8) autobalanced comparators, latches, an encoder, and four buffer storage registers. The second segment converts the five (5)

LSBs and consists of 32 auto-balanced comparators, latches, an encoder, and five buffer storage registers. The MP7683 operates over a wide, full-scale input voltage range from 4.0 volts up to 6.5 volts, full-scale.

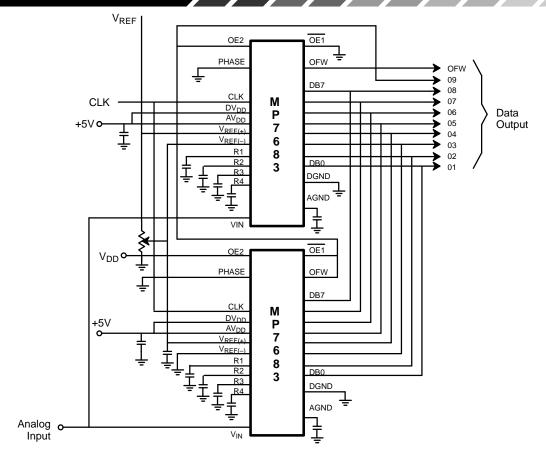

The overflow bit makes it possible to achieve 9-bit resolution by connecting two MP7683's in series. See *Figure 3*.

Specified for operation over the commercial / industrial (-40 to +85°C) and military (-55 to +125°C) temperature ranges, the MP7683 is available in Plastic (PDIP) and Ceramic (CDIP) dualin-line, Shrunk Small Outline (SSOP) and Surface Mount (SOIC) packages.

#### SIMPLIFIED BLOCK DIAGRAM

#### ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.  | DNL<br>(LSB) | INL<br>(LSB) |

|-----------------|----------------------|-----------|--------------|--------------|

| Plastic Dip     | -40 to +85°C         | MP7683JN  | ±1 1/4       | 1 1/4        |

| Plastic Dip     | -40 to +85°C         | MP7683KN  | ±3/4         | 3/4          |

| SOIC            | –40 to +85°C         | MP7683JS  | ±1 1/4       | 1 1/4        |

| SOIC            | –40 to +85°C         | MP7683KS  | ±3/4         | 3/4          |

| SSOP            | –40 to +85°C         | MP7683JQ  | ±1 1/4       | 1 1/4        |

| SSOP            | –40 to +85°C         | MP7683KQ  | ±3/4         | 3/4          |

| Ceramic Dip     | –55 to +125°C        | MP7683SD* | ±1 1/4       | 1 1/4        |

| Ceramic Dip     | –55 to +125°C        | MP7683TD* | ±3/4         | 3/4          |

<sup>\*</sup>Contact factory for non-compliant military processing

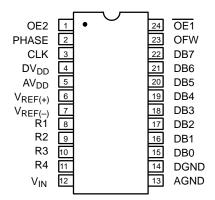

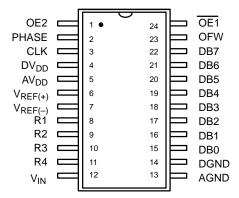

#### **PIN CONFIGURATIONS**

24 Pin CDIP, PDIP (0.600") D24, N24

24 Pin SOIC (EIAJ, 0.335") - R24 24 Pin SSOP - A24

#### **PIN OUT DEFINITIONS**

| PIN NO. | NAME                | DESCRIPTION                      |

|---------|---------------------|----------------------------------|

| 1       | OE2                 | Output Enable Control 2          |

| 2       | PHASE               | Sampling Clock Phase Control     |

| 3       | CLK                 | Clock Input                      |

| 4       | $DV_DD$             | Power Supply                     |

| 5       | AV <sub>DD</sub>    | Power Supply for Analog Circuit  |

| 6       | V <sub>REF(+)</sub> | Reference Voltage (+) Input      |

| 7       | V <sub>REF(-)</sub> | Reference Voltage (–) Input      |

| 8       | R1                  | 1/16th Point of Ladder R Matrix  |

| 9       | R2                  | 5/16th Point of Ladder R Matrix  |

| 10      | R3                  | 9/16th Point of Ladder R Matrix  |

| 11      | R4                  | 13/16th Point of Ladder R Matrix |

| 12      | V <sub>IN</sub>     | Analog Input                     |

| PIN NO. | NAME | DESCRIPTION             |

|---------|------|-------------------------|

| 13      | AGND | Analog Ground           |

| 14      | DGND | Digital Ground          |

| 15      | DB0  | Data Output Bit 0 (LSB) |

| 16      | DB1  | Data Output Bit 1       |

| 17      | DB2  | Data Output Bit 2       |

| 18      | DB3  | Data Output Bit 3       |

| 19      | DB4  | Data Output Bit 4       |

| 20      | DB5  | Data Output Bit 5       |

| 21      | DB6  | Data Output Bit 6       |

| 22      | DB7  | Data Output Bit 7 (MSB) |

| 23      | OFW  | Digital Output Overflow |

| 24      | OE1  | Output Enable Control 1 |

T(§)M

# **ELECTRICAL CHARACTERISTICS TABLE**

Unless Otherwise Specified:  $AV_{DD} = DV_{DD} = 5 \text{ V}$ ,  $F_S = 3 \text{ MHz}$  (50% Duty Cycle),

$V_{REF(+)} = 4.1, V_{REF(-)} = AGND, T_A = 25^{\circ}C$

|                                                                                                                                                                |                                                                                                      |                         | 25°C                                              | Tmin to T                                | max                                        |                                |                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------|------------------------------------------|--------------------------------------------|--------------------------------|------------------------------------------|

| Parameter                                                                                                                                                      | Symbol                                                                                               | Min                     | Typ Max                                           | Min                                      | Max                                        | Units                          | Test Conditions/Comments                 |

| KEY FEATURES                                                                                                                                                   |                                                                                                      |                         |                                                   |                                          |                                            |                                |                                          |

| Resolution                                                                                                                                                     |                                                                                                      | 8                       |                                                   | 8                                        |                                            | Bits                           |                                          |

| Sampling Rate                                                                                                                                                  | F <sub>S</sub>                                                                                       | 0.001                   | 3                                                 | 0.001                                    | 3                                          | MHz                            | For specified accuracy                   |

| ACCURACY (J, S Grades) <sup>1</sup>                                                                                                                            |                                                                                                      |                         |                                                   |                                          |                                            |                                |                                          |

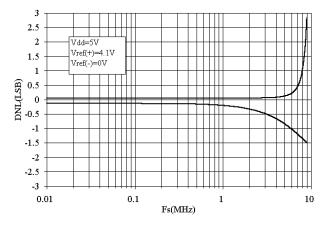

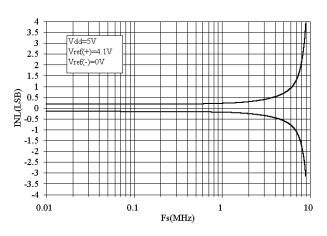

| Differential Non-Linearity<br>Integral Non-Linearity                                                                                                           | DNL<br>INL                                                                                           |                         | <u>+</u> 1<br>1                                   | <u>+</u>                                 | <u>+</u> 1 1/4<br>1 1/4                    | LSB<br>LSB                     | Best Fit Line<br>(Max INL – Min INL) / 2 |

| ACCURACY (K, T Grades) <sup>1</sup>                                                                                                                            |                                                                                                      |                         |                                                   |                                          |                                            |                                |                                          |

| Differential Non-Linearity<br>Integral Non-Linearity                                                                                                           | DNL<br>INL                                                                                           |                         | <u>+</u> 1/2<br>1/2                               |                                          | <u>+</u> 3/4<br>3/4                        | LSB<br>LSB                     | Best Fit Line                            |

| REFERENCE VOLTAGES                                                                                                                                             |                                                                                                      |                         |                                                   |                                          |                                            |                                |                                          |

| Positive Ref. Voltage Negative Ref. Voltage Differential Ref. Voltage <sup>2</sup> Ladder Resistance Ladder Temp. Coefficient <sup>2</sup>                     | V <sub>REF(+)</sub><br>V <sub>REF(-)</sub><br>V <sub>REF</sub><br>R <sub>L</sub><br>R <sub>TCO</sub> | 2<br>AGND<br>4.1<br>500 | 4.1 AV <sub>DD</sub> AV <sub>DD</sub> -AGND  1500 | 2<br>AGND<br>4.1 AV <sub>DD</sub><br>300 | AV <sub>DD</sub><br>5-AGND<br>1950<br>2000 | V<br>V<br>V<br>Ω<br>ppm/°C     | For specified accuracy                   |

| ANALOG INPUT                                                                                                                                                   |                                                                                                      |                         |                                                   |                                          |                                            |                                |                                          |

| Input Voltage Range Input Impedance <sup>2</sup> Input Capacitance <sup>4</sup> Aperture Delay <sup>2</sup> Aperture Uncertainty (Jitter) <sup>2</sup>         | V <sub>IN</sub><br>Z <sub>IN</sub><br>C <sub>INA</sub><br>t <sub>AP</sub>                            | V <sub>REF(-)</sub>     | V <sub>REF(+)</sub> 10 50 55 200                  | V <sub>REF(-)</sub> V <sub>F</sub>       | REF(+)                                     | V p-p<br>MΩ<br>pF<br>ns<br>ps  |                                          |

| DIGITAL INPUTS                                                                                                                                                 |                                                                                                      |                         |                                                   |                                          |                                            |                                |                                          |

| Logical "1" Voltage Logical "0" Voltage Leakage Currents <sup>5</sup> CLK Input Capacitance <sup>2</sup> Clock Timing (See Figure 1.) Clock Period "High" Time | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IN</sub><br>C <sub>IND</sub><br>t <sub>s</sub>          | 3.5<br>333<br>166.5     | 1.5<br><u>+</u> 50<br>5                           | 3.5                                      | 1.5<br><u>+</u> 50                         | V<br>V<br>μA<br>pF<br>ns<br>ns | $V_{IN}$ = DGND to DV <sub>DD</sub>      |

| "Low" Time<br>Duty Cycle                                                                                                                                       | t <sub>l</sub>                                                                                       | 166.5                   | 50                                                |                                          |                                            | ns<br>%                        |                                          |

#### ELECTRICAL CHARACTERISTICS TABLE CONT'D

| Parameter                                                                                                                                                                              | Symbol                                                     | Min | 25°C<br>Typ         | Max                | Tmin to<br>Min | Tmax<br>Max        | Units                                | Test Conditions/Comments                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|---------------------|--------------------|----------------|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL OUTPUTS                                                                                                                                                                        |                                                            |     |                     |                    |                |                    |                                      | C <sub>OUT</sub> =15 pF                                                                                                                      |

| Logical "1" Voltage Logical "0" Voltage Tristate Leakage Data Valid Delay <sup>2</sup> Data Enable Delay <sup>2</sup> Data Tristate Delay <sup>2</sup> Output Capacitance <sup>2</sup> | VOH<br>VOL<br>IOZ<br>t <sub>DL</sub><br>tDEN<br>tDHZ<br>CO | 4.6 | 55<br>20<br>26<br>5 | 0.4<br><u>+</u> 50 | 4.6            | 0.4<br><u>+</u> 50 | V<br>V<br>μA<br>ns<br>ns<br>ns<br>pF | $I_{LOAD} = -1.0 \text{ mA}$ $I_{LOAD} = 2.0 \text{ mA}$ $V_{OUT} = DGND \text{ to DV}_{DD}$ (See Figure 1.) (See Figure 2.) (See Figure 2.) |

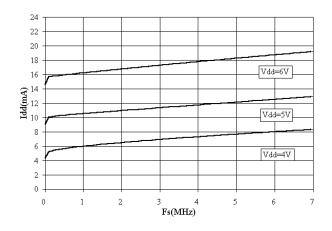

| POWER SUPPLIES  Operating Voltage (AV <sub>DD</sub> , DV <sub>DD</sub> )  Current (AV <sub>DD</sub> + DV <sub>DD</sub> )                                                               | V <sub>DD</sub> <sup>6</sup><br>I <sub>DD</sub>            | 4   |                     | 6.5<br>20          | 4              | 6.5<br>36          | mA                                   | V                                                                                                                                            |

#### **NOTES**

- Tester measures code transitions by dithering the voltage of the analog input (V<sub>IN</sub>). The difference between the measured and the ideal code width (V<sub>REF</sub>/256) is the DNL error. The INL error is the maximum distance (in LSB) from the best fit line to any transition voltage. Accuracy is a function of the sampling rate (F<sub>S</sub>).

- 2 Guaranteed. Not tested.

- Specified values guarantee functionality. Refer to other parameters for accuracy.

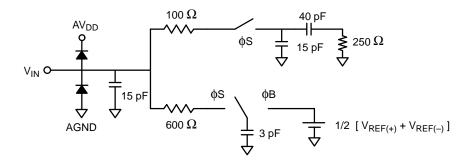

- <sup>4</sup> See V<sub>IN</sub> input equivalent circuit (*Figure 4*). Switched capacitor analog input requires driver with low output resistance.

- All inputs have diodes to DV<sub>DD</sub> and DGND.

- 6 DV<sub>DD</sub> and AV<sub>DD</sub> are connected through the silicon substrate. Connect together at the package and to the analog supply loop.

#### Specifications are subject to change without notice

# ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> (to GND) +6.5 V                         | Lead Temperature (Soldering 10 seconds) +300°C |

|---------------------------------------------------------|------------------------------------------------|

| $V_{REF(+)}$ & $V_{REF(-)}$ GND -0.5 to $V_{DD}$ +0.5 V | Package Power Dissipation Rating to 75°C       |

| $V_{\text{IN}}$ GND –0.5 to $V_{\text{DD}}$ +0.5 V      | CDIP, PDIP, SOIC                               |

| Digital Inputs GND –0.5 to V <sub>DD</sub> +0.5 V       | Derates above 75°C 14mW/°C                     |

| Digital Outputs GND –0.5 to V <sub>DD</sub> +0.5 V      | SSOP                                           |

| Storage Temperature65°C to +150°C                       | Derates above 75°C 10mW/°C                     |

#### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

V<sub>DD</sub> refers to AV<sub>DD</sub> and DV<sub>DD</sub>. GND refers to AGND and DGND.

#### **DEVICE OPERATION**

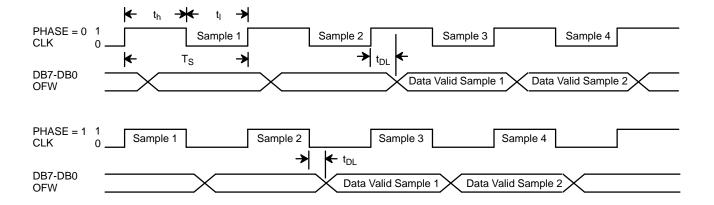

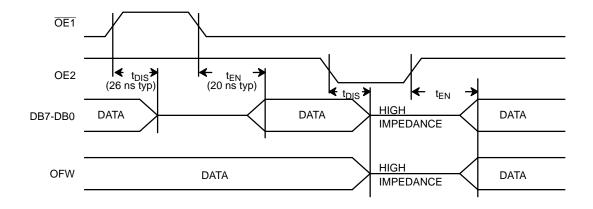

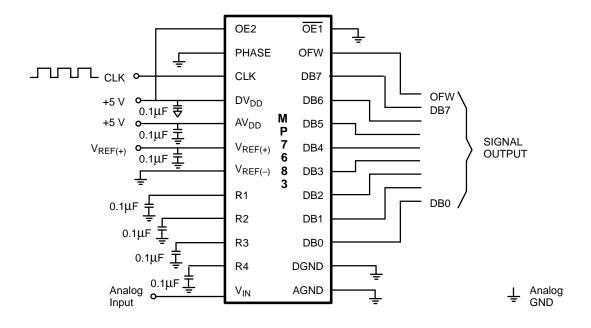

Figure 1. shows the timing diagram of the MP7683 8-bit Flash Converter. A reference voltage is applied between the  $V_{REF(+)}$  and  $V_{REF(-)}$  which drives 256 resistors and switches with 4 voltage taps. These taps drive the inverting inputs of comparators. There are four control lines: Clock,  $\overline{OE1}$ , OE2, and Phase. The phase line determines the polarity of the clock.

Figure 2. shows waveforms with the phase line high and low. With 0 = 1, the "sample" occurs during the high period of the clock cycle and the "auto-balance" occurs during the low period of the clock. The "sample" is queued and pipelined through a series of registers and latches. It appears at the output after 2 clock periods and time delay (Td). After the sample is acquired

the data is valid for every clock period. The  $\overline{OE1}$  will independently disable DB0 through DB7 when it is in a high state. CE2 will independently disable DB0 through DB7 and the OFW buffers when it is in a low state. The Truth Table (*Table 1.*) summarizes this effect.

| OE1 | OE2 | DB7-DB0   | OFW       |

|-----|-----|-----------|-----------|

| 0   | 1   | Valid     | Valid     |

| 1   | 1   | Tri-State | Valid     |

| Х   | 0   | Tri-State | Tri-State |

Table 1. Truth Table

Figure 1. Timing Diagram

Figure 2. Output Enable and Disable Timing Diagram

Figure 3. MP7683 9-Bit Resolution Configuration

Figure 4. MP7683 Typical Connections

#### **APPLICATION NOTES:**

The following information will be useful in maximizing the performance of the MP7683.

- This device may be susceptible to latch-up. All signals must not exceed AV<sub>DD</sub> or AGND, or DV<sub>DD</sub> or DGND at any time. Digital Supply (DV<sub>DD</sub> & AV<sub>DD</sub>) must be applied before all other signals to avoid a latch-up condition.

- The design of a PC layout and assembly will seriously affect the accuracy of the MP7683. <u>Use of wire wrap is not recom-</u> mended.

- The analog input signal (V<sub>IN</sub>) is quite sensitive and should be properly routed and terminated. It should be shielded from the clock and digital outputs so as to minimize cross coupling and noise pickup.

- 4. The analog input should be driven with a buffer op amp ( $Z_{OUT} \le 50 \ \Omega$ ).

- 5. The use of a large shield plane is highly recommended, connected only at one point and connected to virtual ground. The ground plane should act as a shield for parasitics and not a return path for signals. To reduce noise levels, use separate low impedance ground paths.

- 6. The power supplies and reference voltages should be decoupled with ceramic (0.01 to 0.1 $\mu$ F) and tantalum (10 $\mu$ F) capacitors as close to the device as possible.

- 7. The digital output should not drive long wires. The capacitive coupling and reflection will contribute noise to the conversion. When driving distant loads, buffers should be used.

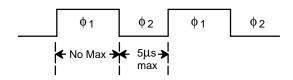

- a. When at 50% Duty Cycle, the minimum clock rate is 100 kHz

- b. When at non-50% Duty Cycle, the minimum clock rate may be DC as long as 2 is kept to less than 5  $\mu$ s.

- 8. To avoid a possible latch-up condition, power should be applied before any input signal is connected.

Figure 5. Analog Input Equivalent Circuit

#### PERFORMANCE CHARACTERISTICS

Graph 1. Supply Current vs. Sampling Frequency

Graph 2. DNL vs. Sampling Frequency

Graph 3. INL vs. Sampling Frequency

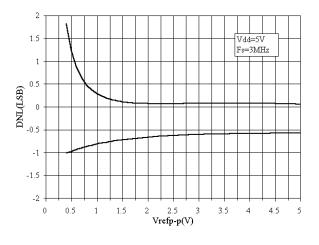

Graph 4. DNL vs. Reference Voltage

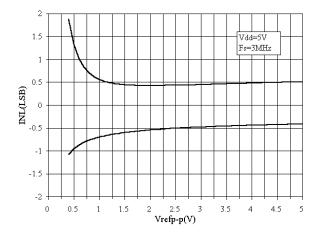

Graph 5. INL vs. Reference Voltage

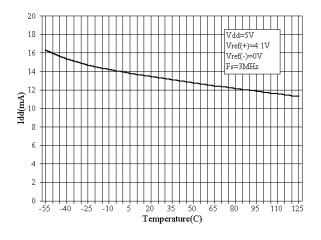

Graph 6. Supply Current vs. Temperature

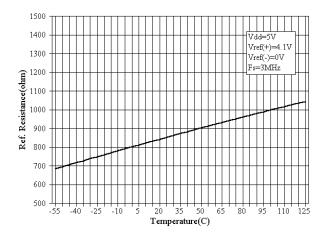

Graph 7. Reference Resistance vs. Temperature

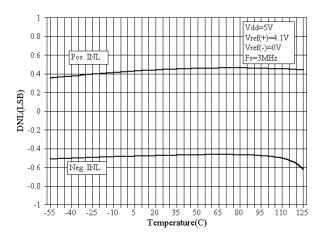

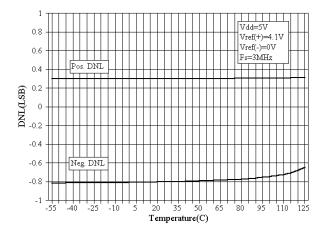

Graph 9. INL vs. Temperature

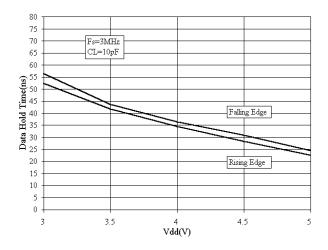

Graph 11. Data Hold Time vs. Supply Voltage

Graph 8. DNL vs. Temperature

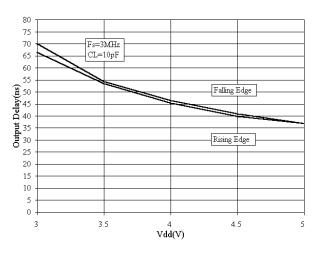

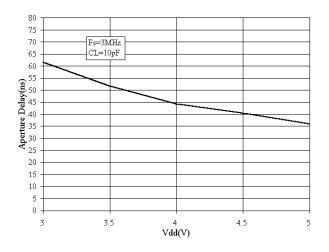

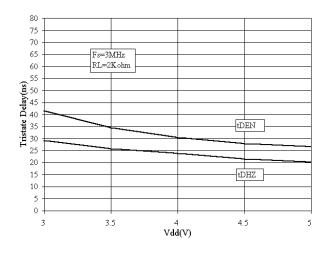

Graph 10. Output Delay vs. Supply Voltage

Graph 12. Aperture Delay vs. Supply Voltage

Graph 13. Tristate Enable Delay vs. Supply Voltage

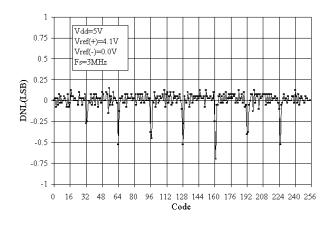

Graph 14. DNL Error Plot

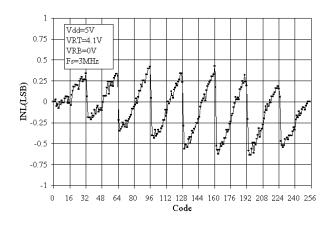

**Graph 15. INL Error Plot**

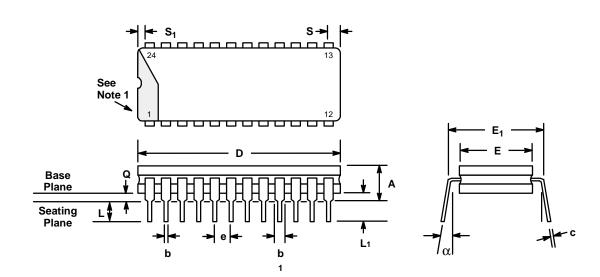

### 24 LEAD CERAMIC DUAL-IN-LINE (600 MIL CDIP) D24

|                | INCHES |        | MILLIN | METERS |       |

|----------------|--------|--------|--------|--------|-------|

| SYMBOL         | MIN    | MAX    | MIN    | MAX    | NOTES |

| А              |        | 0.225  |        | 5.72   |       |

| b              | 0.014  | 0.023  | 0.356  | 0.584  | _     |

| b <sub>1</sub> | 0.038  | 0.065  | 0.965  | 1.65   | 2     |

| С              | 0.008  | 0.015  | 0.203  | 0.381  | _     |

| D              | _      | 1.290  |        | 32.77  | 4     |

| Е              | 0.500  | 0.610  | 12.70  | 15.49  | 4     |

| E <sub>1</sub> | 0.590  | 0.620  | 14.99  | 15.75  | 7     |

| е              | 0.10   | 00 BSC | 2.5    | 4 BSC  | 5     |

| L              | 0.120  | 0.200  | 3.05   | 5.08   | _     |

| L <sub>1</sub> | 0.150  | _      | 3.81   | _      | _     |

| Q              | 0.015  | 0.075  | 0.381  | 1.91   | 3     |

| S              | _      | 0.098  | _      | 2.49   | 6     |

| S <sub>1</sub> | 0.005  | _      | 0.13   | _      | 6     |

| α              | 0°     | 15°    | 0°     | 15°    | _     |

#### NOTES

- Index area; a notch or a lead one identification mark is located adjacent to lead one and is within the shaded area shown.

- 2. The minimum limit for dimension  $b_1$  may be 0.023 (0.58 mm) for all four corner leads only.

- 3. Dimension Q shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- The basic lead spacing is 0.100 inch (2.54 mm) between centerlines.

- 6. Applies to all four corners.

- 7. This is measured to outside of lead, not center.

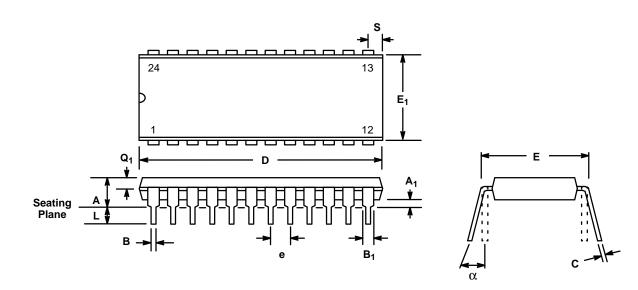

# 24 LEAD PLASTIC DUAL-IN-LINE (600 MIL PDIP) N24

|                    | INC   | HES    | MILLIN | METERS |

|--------------------|-------|--------|--------|--------|

| SYMBOL             | MIN   | MAX    | MIN    | MAX    |

| А                  |       | 0.225  |        | 5.72   |

| A <sub>1</sub>     | 0.015 | _      | 0.38   |        |

| В                  | 0.014 | 0.023  | 0.356  | 0.584  |

| B <sub>1</sub> (1) | 0.038 | 0.065  | 0.965  | 1.65   |

| С                  | 0.008 | 0.015  | 0.203  | 0.381  |

| D                  | 1.160 | 1.290  | 29.46  | 32.77  |

| Е                  | 0.585 | 0.625  | 14.86  | 15.88  |

| E <sub>1</sub>     | 0.500 | 0.610  | 12.70  | 15.49  |

| е                  | 0.10  | 00 BSC | 2.5    | 4 BSC  |

| L                  | 0.115 | 0.150  | 2.92   | 3.81   |

| α                  | 0°    | 15°    | 0°     | 15°    |

| Q <sub>1</sub>     | 0.055 | 0.070  | 1.40   | 1.78   |

| S                  | 0.040 | 0.098  | 1.02   | 2.49   |

Note: (1) The minimum limit for dimensions B1 may be 0.023" (0.58 mm) for all four corner leads only.

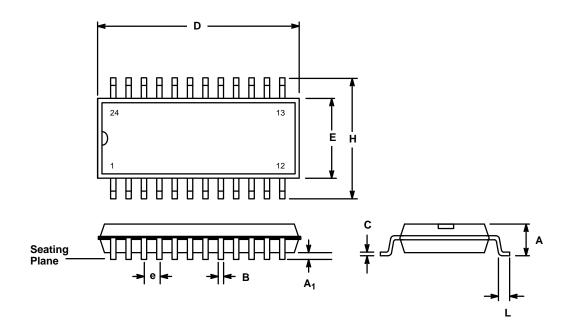

## 24 LEAD SMALL OUTLINE (335 MIL EIAJ SOIC) R24

|        | MILLIN | IETERS      | INC   | CHES      |

|--------|--------|-------------|-------|-----------|

| SYMBOL | MIN    | MAX         | MIN   | MAX       |

| А      | 2.60   | 2.80        | 0.102 | 0.110     |

| A1     | 0.2    | 2 (typ.)    | 0.00  | )8 (typ.) |

| В      | 0.3    | 0.50        | .012  | 0.020     |

| С      | 0.10   | 0.20        | 0.004 | 0.008     |

| D      | 15.0   | 15.4        | 0.590 | 0.606     |

| Е      | 8.3    | 8.5         | 0.327 | 0.335     |

| е      | 1.2    | 1.27 (typ.) |       | 60 (typ.) |

| Н      | 11.5   | 12.1        | 0.453 | 0.477     |

| L      | 0.8    | 1.2         | 0.031 | 0.047     |

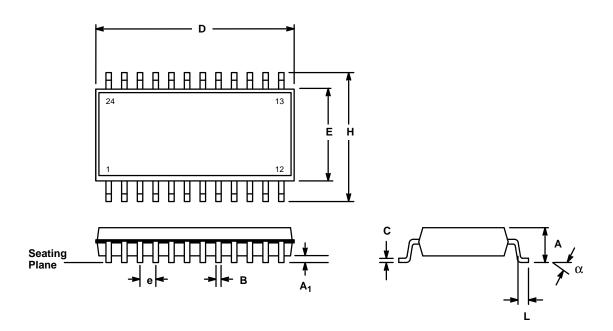

# 24 LEAD SHRINK SMALL OUTLINE PACKAGE (SSOP) A24

|                | MILLI | METERS | INC   | CHES   |

|----------------|-------|--------|-------|--------|

| SYMBOL         | MIN   | MAX    | MIN   | MAX    |

| Α              | 1.73  | 2.05   | 0.068 | 0.081  |

| A <sub>1</sub> | 0.05  | 0.21   | 0.002 | 0.008  |

| В              | 0.20  | 0.40   | 0.008 | 0.016  |

| С              | 0.13  | 0.25   | 0.005 | 0.010  |

| D              | 8.07  | 8.40   | 0.318 | 0.331  |

| Е              | 5.20  | 5.38   | 0.205 | 0.212  |

| е              | 0.65  | BSC    | 0.02  | 56 BSC |

| Н              | 7.65  | 8.1    | 0.301 | 0.319  |

| L              | 0.45  | 0.95   | 0.018 | 0.037  |

| α              | 0°    | 8°     | 0°    | 8°     |

# **Notes**

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright EXAR Corporation Datasheet April 1995

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

**T**@M"